# Evolvable Hardware for Autonomous Systems

Adrian Stoica

Jet Propulsion Laboratory

adrian.stoica@jpl.nasa.gov, 818-354-2190, ehw.jpl.nasa.gov

JPL Co-investigators: D. Keymeulen, R. Zebulum, M.I.Ferguson, T. Daud, T. Arslan (Visiting Prof – U Edinburgh)

GECCO-2005

EHW for flexibility and survivability of autonomous systems JPL/NASA driver - long-life spacecraft Dramatic changes in hardware/environment, e.g. in case of faults or need for new functions, may require in-situ synthesis of a totally new hardware configuration. Versatility: Create new Survivability: Maintain functionality functionality required by coping with changes in changes in requirements or HW characteristics environment · Radiation impacts New functions required for · Temperature variations new mission phase or Aging · Malfunctions, etc. Up-link new functions for re-planned mission Accurate model of hardware is not available after launch

Develop space HW that can evolve

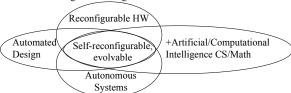

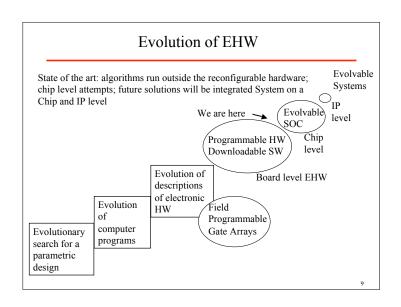

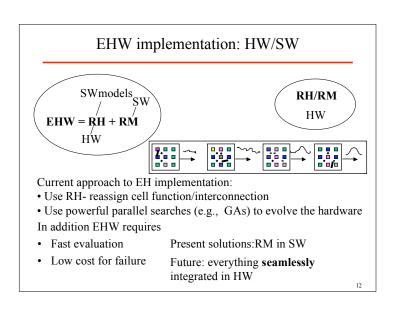

# Evolvable Hardware (EHW) Technology Evolvable Hardware = Reconfigurable HW + Reconfiguration Mechanism

In a narrow sense (EHW) is programmable hardware self-configurable by built-in Evolutionary Algorithms.

FPA +GA

#### HW that can change

- AntennasElectronics

- MEMS

- BioMEMS

# Mechanism controlling the change

- search/optimization

- algorithmic

- · knowledge-based

<u>intelligent part</u> – the built-in mechanisms controling the adaptation/self-configuration

2

#### EHW: definitions

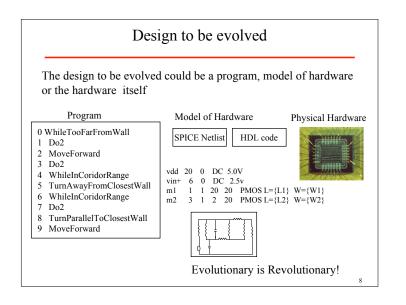

· Intelligent automatic design of reconfigurable hardware...

- Objective: development of flexible and survivable HW capable of intelligent self-configuration, self-tuning, and self-repair, that can can adaptively change through reconfiguration/compensation for optimal signal processing, sensing/control, and survival in the presence of faults/degradation.

- Successful applications: in automated design, automated calibration and tuning, in-field adaptation of hardware systems, sensing, control and robotics.

#### **Tutorial Overview**

- · Introduction to EHW

- Algorithms for self-configuration and evolution

- · Reconfigurable and Morphable Hardware

- Demonstrations of Evolvable Systems

- Application Examples

- System Aspects

- · Resources for EHW Engineers

A new generation of hardware A third generation hardware in terms of flexibility and fault tolerance Flexibility, fault-tolerance + Automated Design Self-reconfigurable, evolvable +Artificial/Computational Intelligence Reconfigurable BISR Fixed HW Built-in self-repair Generation 2nd 3rd

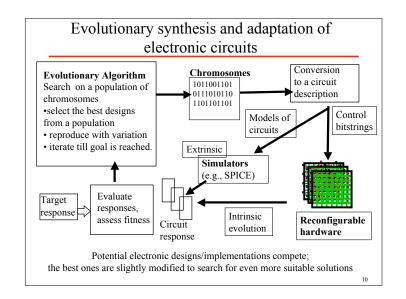

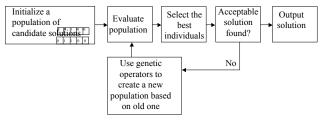

#### Mechanisms for reconfiguration: evolutionary algorithms "Design" goal: survival The most fit individuals Evolution in nature survive becoming parents; has lead to species children inherit parents highly adapted to characteristics, with some their environment: variations, and may perform adaptation ensured better, increasing the level survival. Millions of years of adaptation. Design goal: meet system specifications Potential designs Same evolutionary compete; the best ones principles are slightly modified to can be applied to search for even more machines. suitable solutions. Accelerated evolution, ~ seconds for electronics

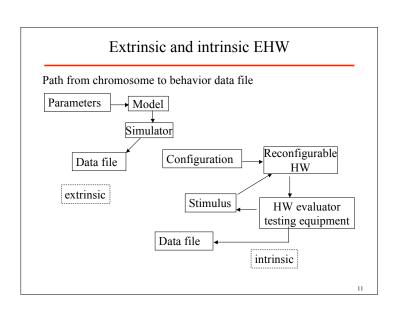

## Evolution in Simulations vs Evolution in Hardware

- Computationally intensive (640,000 individ. for ~1000 gen.)

- 10s of hours, expected ~3 min in 2010 on desktop PC for experiments in the book (~50 nodes)

- SPICE scales badly (time increases nonlinearly with as a function of nodes in netlist - in ~ subquadratic to quadratic way)

- No existing hardware resources allow porting the technique to evolution directly in HW (and not sure will work in HW)

- JPL's VLSI chips allow evolution 4+ orders of magnitude faster than SPICE simulations on Pentium II 300 Pro.

- ~ 10s of seconds in 2002 for circuits of complexity >= Koza's).

13

#### Inspiration

NN seek biological inspiration for

for certain problems where biology does

- computational elements,

- architecture

- mechanisms

EHW seeks biological inspiration for methodology leading to designs (1,2) appropriate to situations/application

- 1. of various types of HW

- freeing from biological constraints

Building block

• NN: Simplified/distorted models of biological neuron

• EHW: Domain oriented reconfigurable cell

14

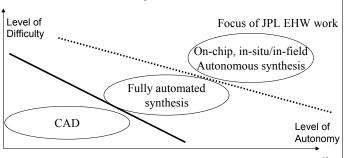

#### On-chip EHW vs CAD/synthesis tools

EHW could overcome fabrication mismatches, drifts, temperature and other plagues to analog, exploiting the actual on-chip resources – finding a new circuit solution to the requirements with given constrains and actual on-chip resources.

#### Algorithms for self-configuration and evolution

- General perspective on search, optimization and adaptation algorithms

- Essence of evolutionary algorithms

- Details of operation of Genetic Algorithms

- Multi-criteria optimization, Hybrid Search

# Algorithms for reconfiguration. Objectives: control self-configuration for desired functionality

- A control C that creates a structure / topology / architecture S, that has the function F. Specification in terms of S or F. F may include constraints, preferences, etc.

- Behavior/Function may change in time, in simple case it doesn't

- Often C, even for a set of states which can be decomposed, but could be a sequence C1 C2 C3 if system has memory

- Digital or analog controls (analog signals often obtained by conversion from digital)

17

#### Principles of evolutionary processes

- Genetic program (genotype) -> expressed behavioral traits (phenotype)

- Pleiotropy: a single gene may simultaneously affect several phenotypic traits.

- Polygeny: a single phenotypic characteristic may be determined by the simultaneous interaction of many genes.

- Epistasis: expression of one gene masks the phenotypic effects of another

- There are no one-gene, one-trait relationships in naturally evolved systems.

- Very different genetic structures may code for equivalent behaviors; various circuits that implement a function with electronic components.

Search/optimization algorithms and NFL Theorems

- Start with an initial "guess" at a solution, which is updated over iterations

with the aim of improving the performance measure (objective function).

- Multiple variables influence the function: a multivariable optimization problem of minimizing or maximizing an objective function.

- No free lunch Theorem: No search algorithm is uniformly better than all

other algorithms across all possible problems. (Cheaper lunches in certain

places: Some algorithms may work better than others on certain classes of

problems as a consequence of being able to exploit the problem structure.)

- E.g. traditional nonlinear programming methods (e.g., constrained conjugate

gradient) are well suited to deterministic optimization problems with exact

knowledge of the gradient of the objective function; more generally,

stochastic gradient methods are effective if one has direct (unbiased)

measurements of the gradient of the objective function.

18

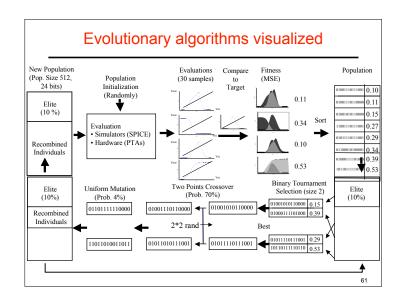

#### Principle of operation of evolutionary algorithms

Coding solutions as chromosomes. Operates on code not on solution. A string is a candidate solution.

- •Switch states 11011 Bitstring

- •Program (+x(\*x (-x 1)))

- •Vector (4.3 3.2 500)

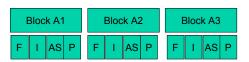

#### From code to instantiation

- F=Function, I= Interconnect of terminals, AS= Analog Signal, P=Parameter of passive component

- Example for Block A1: 101 0101 1000 0011 101 1111

- F= 101 (e.g. 2 input Amp with gain g1, out of 8 choices)

- I: 0101 1000 0011 (eg 2 in and 1 out, NESW connections In 1 from E W, In 2 from N, Out goes to S and W

- Analog Signal: 101 An analog bias of 6/8 on bias node

- Parameter of passive component: 1111 selection of 10k R

21

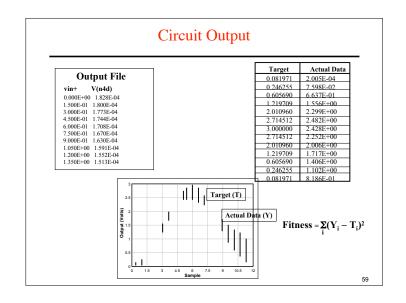

#### **Objective Functions**

Objective function evaluates how well each individual performs. Goal: maximize the objective function Standard Method: compute a distance to a target

$$F = \sum_{i=0}^{n-1} (W_i \cdot |R_i - T_i|)$$

Fitness F is computed over n samples;

R<sub>i</sub> – Individual Response;

$T_i-Target\ Response;$

W<sub>i</sub> - Weights reflecting some knowledge of the problem

The design of a good fitness evaluation function is critical for evolution.

23

#### Measurement and evaluation of individuals

- Testbench, or in-system measurement:

- Stimulation signals

- Load on the output signals

- Measured in the testbench:

- Time response, taking samples (Often A/D conv for processing in digital

- Frequency response, (directly (Spectrum Analyzer), indirect (FFT)

- Other measures, such as current from source

- Effects: derived effects (if electrical device controls something else)

- Quality of an individual: an overall fitness value is determined based on individual fitness function associated to the testbench, and their weighting.

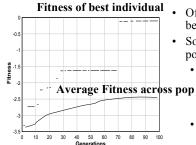

Improvement in individual and population

Example of improvement in fitness of the best individual over the generations (and

- Often we care only of best individual

- Sometimes we care of a population:

- For monitoring purposes to understand better what is going on

- For fault-tolerance we may want several good "mutants" – a fault gives a mutant which still has high fitness

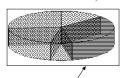

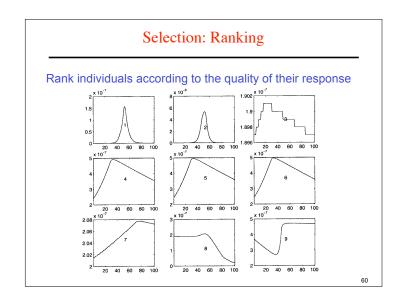

#### Selection

- Based on the principle of survival of the fittest;

- Better candidate solutions get more offspring with

- same/close genetic code

- •Deterministic in ES and EP;

- Probabilistic in GA and GP

Proportional Selection Roulette wheel selection

Spin the roulette

Those who have higher fitness have higher probability to be selected for mating

- •Selection Techniques:

- Proportional Selection;

- ·Rank based selection;

- ·Exponential Selection;

- ·Tournament Selection;

Slice in roulette and fitness of an individual are proportional

25

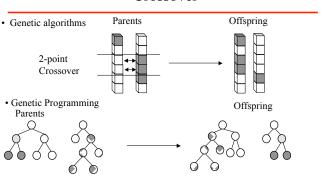

#### Crossover

- Recombination of genetic material that contributes to the variability in the population;

Harmful effects: destroying potentially useful building blocks

- •Automatically Defined Functions (ADFs): protection against disruptive effect of crossover.

26

#### Schemata, building blocks, ADFs

- GA/GP (EAs using crossover) use the building block theory useful components of what makes a solution (chunks of chromosomes) can be efficiently manipulated and used to lead to the solution.

- A problem decomposition

- Looking for similarities patterns in chromosomes of similarly performing solutions

- 1100 10

- 0010 3

- 0101 4

- 1101 20 11xx (or 110x) may be a good building block -schemata set of all combinations based on same pattern

- Goldberg: Ensure BB supply, growth, understand BB spead, ensure good BB decisions, know BB challenges, ensure good BB mixing

- Crossover probability rules of thumb

27

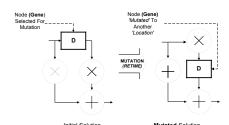

#### Mutation

- Each bit of a new string can be changed (mutated) with a probability given by the *mutation rate*;

- Low values for the mutation rate are often used;

- Traditional interpretation: only support for crossover;

- More recent voices: driving force of GAs: (something other EA camps have always stated) (or it depends on problem/rep)

- GAs performance largely affected by the mutation rate.

#### Adaptive operators

- Adapting the probability associated to evolutionary operators improves convergence

- · Crossover probability

- Mutation probability

- Change representation

- Change selection probability and method all is permitted

29

#### Population, generations, runs

- Fixed or variable population size

- Small populations more generations, vice-versa

- ~ 100 individuals very common

- Usually GP asks for more: eg 640,000 in some of Koza's experiments

- Hundreds of generations

- Sampling a small % of space

- See if it is still improving tracing amount of changes in last generations

- Stop: nr of generations, time, lack of improvement

- · Re-start, change initial population, seed with solutions

11

#### Specific Crossover and Mutation

**Example of Mutation Operation**

Examples from T. Arslan's work

30

#### Multi-criteria optimization, trade-offs, Pareto optimality

- The simultaneous optimization of multiple, possibly competing, objective functions deviates from the single-function optimization in that it seldom admits a perfect (or Utopian) solution;

- Instead, multi-objective optimization problems tend to be characterized by a family of alternatives that must be considered equivalent in the absence of information concerning the relevance of each objective relative to the others:

- Two different methods: Plain aggregating approaches and Pareto-based approaches;

- Plain aggregating approaches perform the scalarization of the objective vectors: each objective, f<sub>i</sub>(x), multiplied by the weight w<sub>i</sub>.

$f(x) = \sum_{i=1}^{n} w_i f_i(x)$

Pareto: A is superior to B if in all objectives A is better or equal to B

e.g. compare houses by price, lower interest, safer neighborhood

A \$200k, 6%, 1/5 B \$300k, 6%, 1/5, C \$300k 5% 2/5

A and C solutions on Pareto front

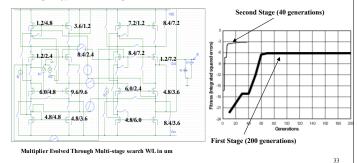

#### Multi-stage search: Search for topology followed by parameter optimization (multi-method ok)

- First Stage: GA-based Evolution of the circuit topology;

- · Second Stage: GA-based Optimization of the transistor sizes for the best topology resulted in the first stage. Initialization is made with the best topology and random parameters.

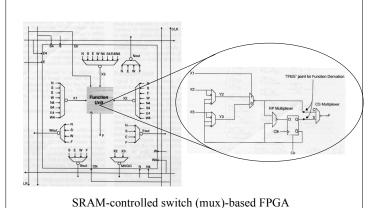

- Function change by configuration change

- · Switch-based devices, switches interconnecting functional modules of primitive functions (logical or analogical)

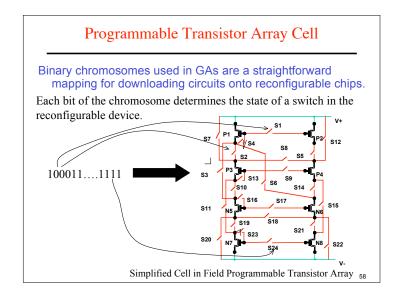

Reconfigurable Devices, Tools, Potential for EHW

- Vendor programming tools allow switches to be turned ON/OFF, in a mode visible or invisible to user, via intermediary program conversions.

- Determining the status of the switches, which switches are ON (OFF) is the search/optimization problem for EHW. Either a local search for compensation; variations around a configuration determined by knowledge/analytical means, or, a new configurations needs to be searched e.g. when unidentified faults prevent mapping of computed solutions

- Status of switches on or off can be straightforward associated with a binary representation used by genetic algorithms

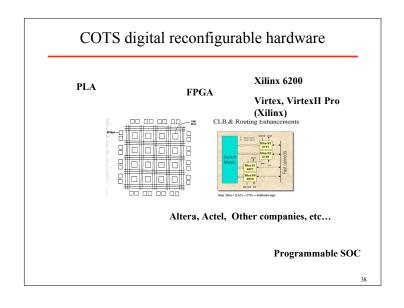

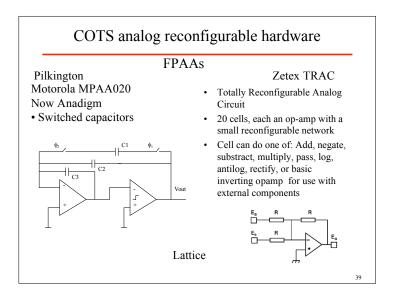

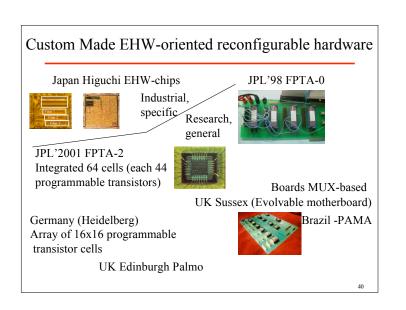

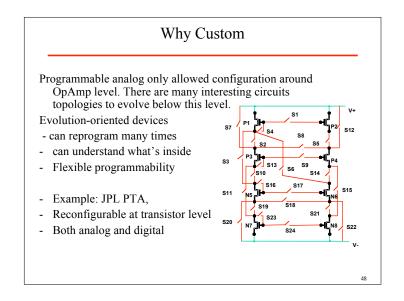

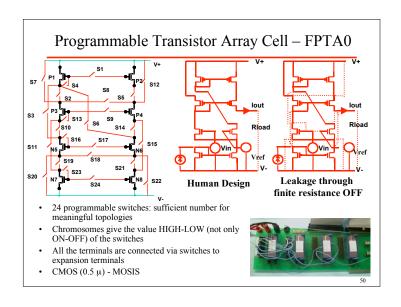

#### Reconfigurable Hardware

- Reconfigurable hardware (switch-based). Devices, SW Tools, Potential for EHW

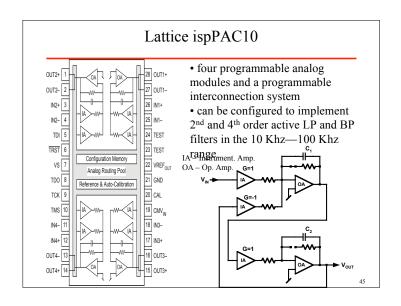

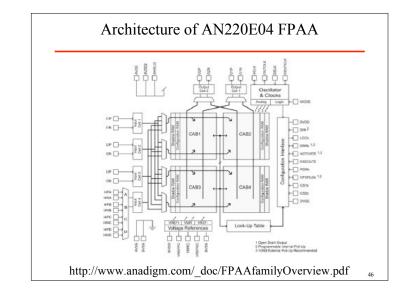

- Field Programmable Gate Arrays (FPGA) Xilinx examples

- Field Programmable Analog Arrays (FPAA) Anadigm Examples

- Field Programmable Transistor Arrays (FPTA) JPL examples

#### Reconfigurable hardware is hardware that changes cell function and cell interconnect

Language for programming reconfigurable hardware needs to define: Alphabet -choices of cells

Vocabulary/Grammar – rules of interconnect

Genetics:  $\{G,A,T,C\}$  (GATTACA) IBM Computer:  $\{1,0\}$  (1010011)

FPGA: AND, OR, NOT

FPTA: Cells of Transistor Arrays

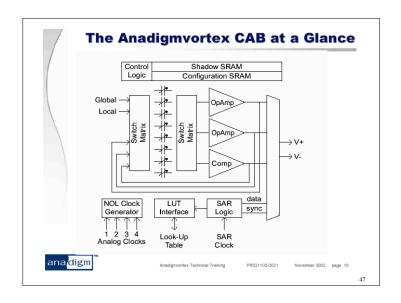

#### Configurable Mixed-Signal Array

The PSoC<sup>TM</sup> CY8C25122/CY8C26233/CY8C26443/CY8C26643 family of programmable system-on-chip devices makes multiple MCU-based system components with one single-chip, configurable device.

A PSoC device includes configurable analog and digital peripheral blocks, a fast CPU, Flash program memory, and SRAM data memory in a range of convenient pin-outs and memory sizes.

The driving force behind this innovative programmable system-on-chip comes from user configurability of the analog and digital arrays: the PSoC blocks.

Example Applications on the PSoC (Application notes on www.cypress.com)

- · PSoC Single-Phase Power Meter Reference Design

- · Modem 300 Baud

• Magnetic Card Reader Reference Design

Cypress CY8C26443 Final Datasheet May. 29, 2003

41

#### Cellular Architecture in Xilinx 6200 chip

- · Architecture, transparence

- NESW

- Can take any bitstring

- · configuration switches

- Routing short links with neighbours, long busses skipping over areas, hierarchy of routing resources,

- configurable blocks LUT one of 8/16 of 2/3 input gates

- RAM

42

#### Xilinx XC6200 cell

.

Tone-Discriminator for 1 kHz and 10 kHz using Transistors

1kHz - 10KHz

0 1

## Thompson's experiment

- Adrian Thompson @ Sussex U.

- · Frequency discriminator

- 10x10 corner of FPGA Xilinx 6200, no clk

- Conventional design searches in constraint regions

- · EA can explore larger space, possibly better solution

- · Evolution of robust circuits:

Use of FPGAs from different foundries, at different temperatures

Researchs

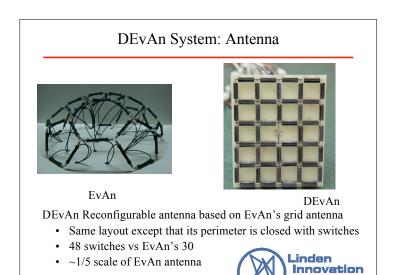

• ~1/5 scale of EvAn antenna

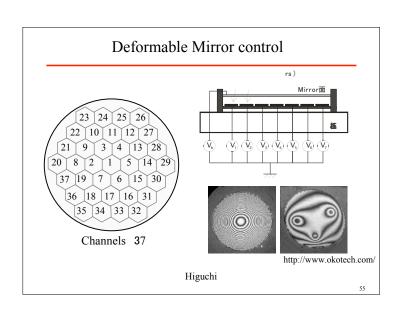

#### Evolvable Femtosecond Laser System - Higuchi Laser alignment can be optimized autonomously by genetic algorithms to obtain the maximum output Laser Cavity -GA(CPU) Chromosomes Especially Suitable for -Motor Controller-1. Laser Processing for Diamonds and Advantages: 1. Autonomous Adjustment Shape-memory-alloy 2. Portable Size 2. Medical Treatment 3. Ultrashort pulse (~10<sup>-15</sup>sec) (e.g. macula, depilation)

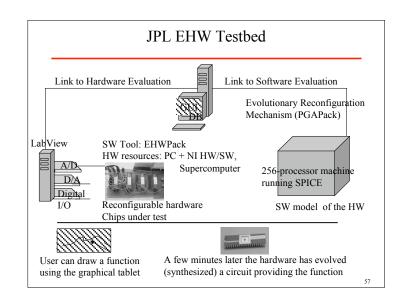

#### Demonstrations of Evolvable Systems

- · Evolution on JPL EHW Testbed

- Details of EHW Pack (SW tools)

- · Platform for mixtrinsic evolution

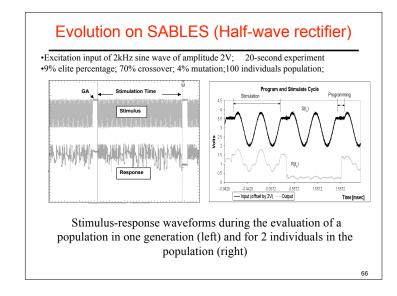

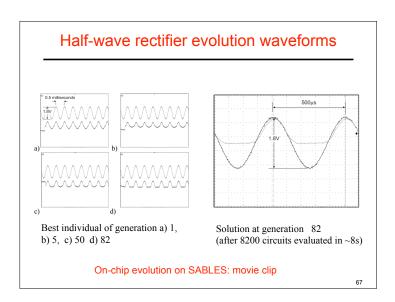

- · Evolution on JPL SABLES (Stand-Alone Board-Level Evolvable System)

- · Half-Wave rectifier

On-chip evolution and fault-recovery: movie clip

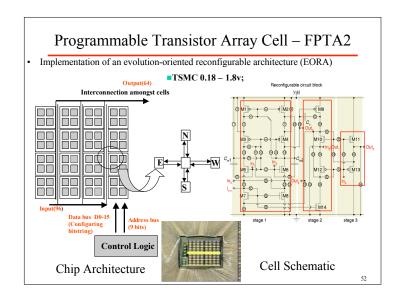

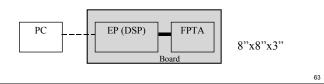

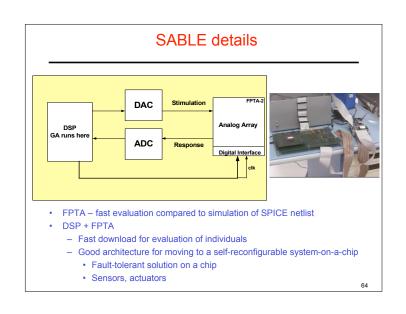

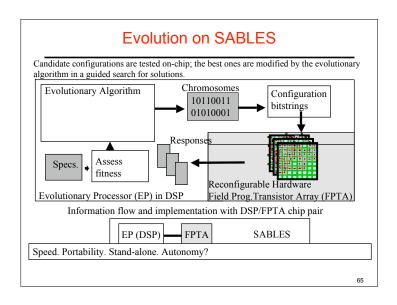

#### Structure of SABLES

- Reconfiguration mechanism (evolutionary algorithm): TI DSP;

- Reconfigurable Hardware: Field Programmable Transistor Array (FPTA2)

- Performance: 1-2 orders of magnitude reduction in memory, 4+ orders of magnitude improvement in speed compared to systems evolving in simulations.

#### **Application Examples**

- · Design for post-fab compensation/calibration

- Design for implementation/fabrication

- · Compensation at extreme temperatures

- Fault-tolerance and fault-recovery

- · Evolvable antennas

- Adaptive filters

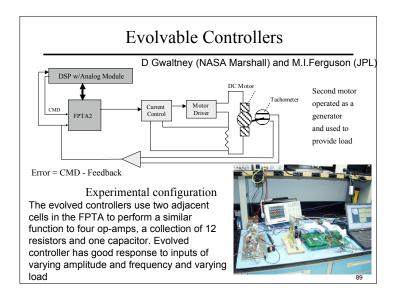

- · Evolution of controllers

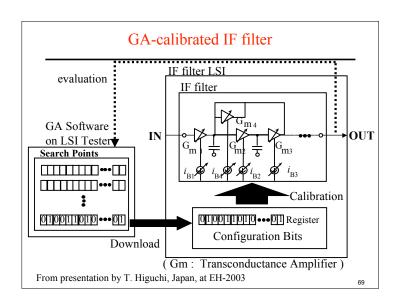

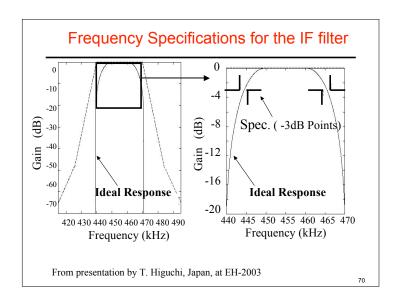

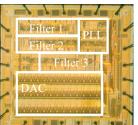

#### Results of GA-calibrated IF Filter Chip

On-chip calibration reduces the need for "over-design" and introduction of conventional compensation circuits. In this way there is les circuitry, which takes less power.

Filter area was reduced by 63%

Power dissipation reduced by 26%

Yield rates improved (97%)

This approach can be applied to a wide variety of analog circuits Good approach for low feature size!

71

Photo of the die

From presentation by T. Higuchi, Japan, at EH-2003

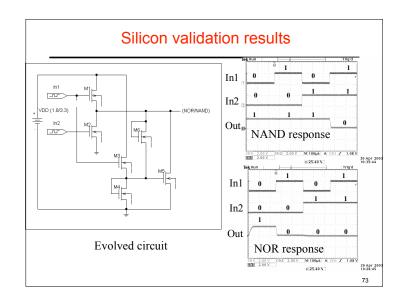

#### Silicon validation results

- Several circuits evolved at transistor level and then fabricated on a prototype ASIC on a HP 0.5 micron process;

- Circuit representation: the chromosome encodes the circuit topology (MOS transistor connections) and the transistors' sizes (width and length);

- Number of components was imposed, or limited to maximum 8;

- Most experiments used populations of 40 individuals and a number of 400 generations.

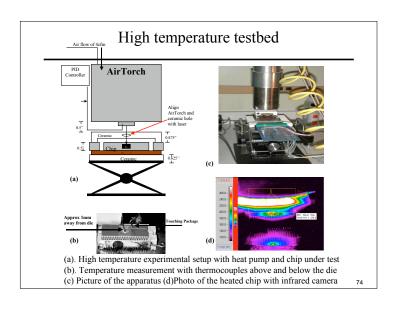

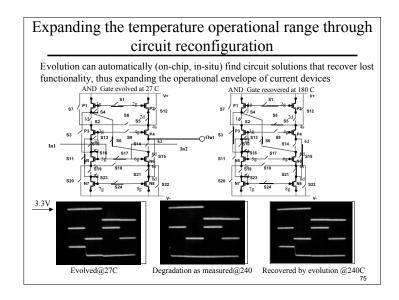

## Coping with faults and degradation in extreme environments

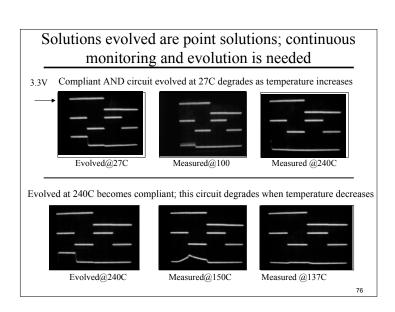

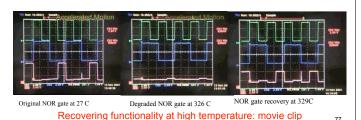

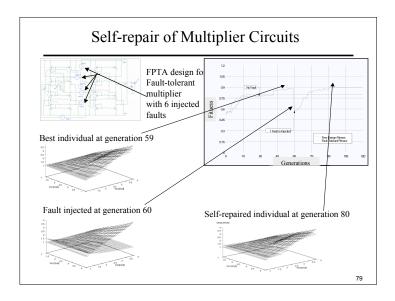

Evolution can recover functionality of circuits affected by faults and degradation, by finding a new circuit bypassing the fault or using damaged components in a different configuration. Experiments at low (-196 C) and high (>+300 C) demonstrate that electronic functions altered by temperature can be recovered through reconfiguration.

# Circuits designed specifically for high temperatures (only) Evolve circuits that work at temperature beyond that of conventional cells Overling the perameters (W/L) Overling the peram

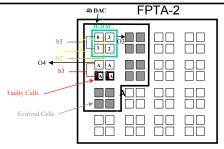

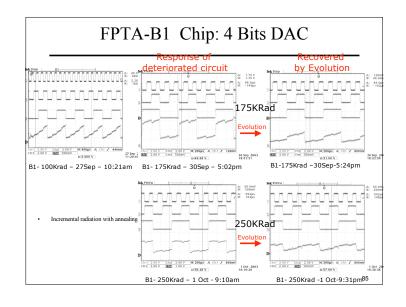

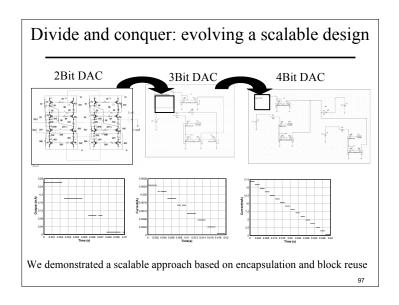

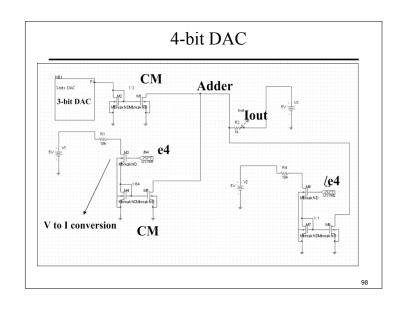

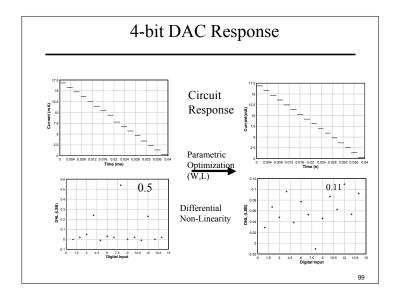

#### Self-repair of Digital to Analog Converters

- Hardware experiments using FPTA-2 chip;

- Evolve first a 2-bit DAC, using it as a building block to evolve a 3-bit DAC, and reusing it to evolve a 4-bit DAC.

- Total number of FPTA cells: 20

- 4 cells mapping a previously evolved 3-bit DAC (evolved from a 2-bit DAC);

- 4 cells mapping human designed Operational Amplifier (buffering and amplification);

- 12 cells have their switches' states controlled by evolution.

- Fault application: open all the switches of 2 cells of the evolved circuit;

#### Self-repair of Digital to Analog Converters

- Faulty Cells (Black): All switches opened (stuck-at 0 fault);

- 3-bit DAC Cell: Cells '0', '1', '2' and '3' map the previously evolved 3-bit DAC, whose output is O3.

- OpAmp Cell (Label 'A'): constrained to OpAmp implementation

- Evolved Cell (Grey): switches' states controlled by evolution.

- O4 is the output of the 4-bit DAC.

81

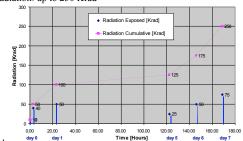

# Radiation Tolerant Experiments: Protocol

- Total Ionization Dose (TID)

- Radiation type: electrons Beam from accelerator

- High Radiation Rate (HRD): 300 rad/sec

- Particle energy: 1MeV

- Bias: chip power on and input/output connect to Vdd and Gnd.

- Circuit Level Analysis: Rectifier, NAND, 4bits DAC

- Cumulative Effect Expected:

- Shift of threshold voltage (silicon dioxide effect)

- Leakage current (Field Oxides effect)

83

#### Fault-Tolerant data converter (4bit DAC): responses In2 In3 In3 04 04 Response of Best Evolved Circuit Ch3 5.00 V (HZ 3.00 V ii 58.00 % Recovery by Evolution of 4bit DAC: In1 • 12 Cells used by evolution In2 • 2 Cell constrained to OpAmp 04 • 4 Cells constrained to 3bit DAC • 2 Faulty Cells • Input: 10 kHz - Sampling: 20 kHz Response of recovered circuit • Full-Scale Output Voltage: 0.6 Volt

## Radiation Experiments: Circuits

Cumulative Radiation: up to 250 Krad

- · Circuits Tested:

- Switching Element (Transmission Gates): Recovery of Identity at 250Krad

- Analog Signal: Recovery of Rectifier at 100, 175 and 250Krad

- Logic Signal: Recovery of NAND gate at 175 and 250 Krad

- Mixed Signal: Recovery of 4bits DAC at 175 and 250 Krad

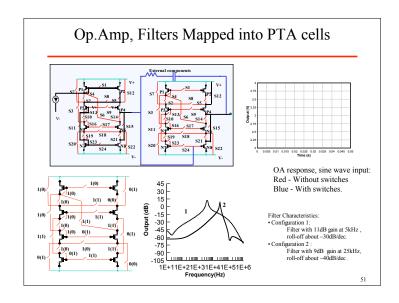

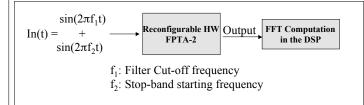

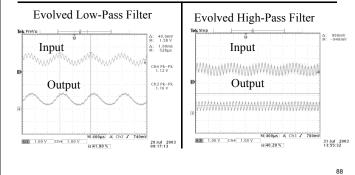

#### **Evolution of Filters**

- Binary representation used both in simulation and HW experiments:

- Simulation experiments using SPICE models of the first FPTA chip;

- Hardware experiments using FPTA-2 chip;

- Circuits evaluated in the frequency domain:

- Simulation: small signal analysis in SPICE;

- Real hardware: FFT of the circuit transient response.

#### Filter Evolution in Hardware

- Reconfigurable device: FPTA-2

- Experiments performed on SABLES platform: about 5 minutes evolution time;

Fitness function maximizes output FFT component at f<sub>1</sub> and minimizes the one at  $f_2$ .

87

#### Filter Evolution in Hardware

- Low-pass  $(f_{1/2} = \overline{1kHz/10kHz})$  and high-pass filters  $(f_{2/1} = 1 \text{kHz}/10 \text{kHz});$

- Use of 10 cells of the FPTA-2 chip;

#### System Aspects

- Integration

- Need for upfront complete specifications

- Behavioral vs structural specification

- · Languages for evolvable hardware

- Verification and validation

- · On-line vs off-line evolution

- · Techniques to reduce evaluation time

90

#### Revisiting Challenges and open Problems

- It is still hard to evolve complex circuits, although we can evolve now orders of magnitude faster.

- It is hard to prove a solution is stable, robust, and hard to predict its behavior outside the domain in which it was evolved.

- The difficulty is in writing fitness functions and guiding evolution for complex systems

- · Complete upfront Specifications are required

- The challenge of conventional design is replaced with that of designing an evolutionary process that automatically performs the design in our place. *This may be harder than doing the design directly*, but makes autonomy possible.

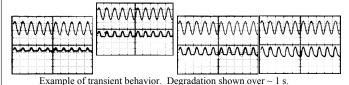

On-chip search may suffer from Transient

Solutions and Memory Effects

- Circuit under evaluation my require a certain amount of time to achieve steady state, while faster evaluation may evaluate a transient behavior

- FPTA-state dependence: Behavior exhibited in the evaluation can be influenced by the circuit downloaded previously;

- Artifacts due to parasitic as well as static capacitors in the chip which can be charged during one configuration period and not discharged before the next configuration is tested;

- · Observation: GA usually eliminates transient solutions after some generations.

92

#### Solution is guarantied only where tested

Circuit evolved at 2kHz does not work at more than 10kHz

Response of the half-wave rectifier for a frequency sweep from 500Hz to 5kHz(left).

Deteriorated response at 50kHz.

Circuit behavior should be evaluated for the overall frequency domain in which it is expected to work

93

## Evolution does not work on implicit assumptions

Evolutionary design requires explicit formulation of assumptions often implicit to human designers. For example:

- evolved logic gates tested with slow signals were naturally slow

- · Evolution in small timescales: transient solutions;

- · Evolution in large timescales: slow gates;

#### Solutions:

- · Mixtrinsic evolution: using combined excitation modes;

- Increase the duration of transient analysis to 'catch' operating point;

- Decrease step of transient analysis: check circuit behavior after transition;

- Increase output load to ensure a fast gate.

Evolved NAND gate evaluated in the timescale of microsecond (until 10-5 sec)

94

#### Challenges ...and how we address them

- · Scalability

- Existence/convergence of optimal solution

- · Satisfying real world requirements

- loads, power

- · Understandability

- · Complete specifications

- · Hardware Artifacts

- · Hierarchy

- Representations, adaptive GA parameters

- Smart fitness

Evolve sensors rather than controls

95

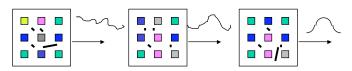

## Addressing complexity by hierarchical design

· Design and reuse Evolve a simpler function, encapsulate the result, reuse- use as primitive. 3-bit DAC

• Use a standard higher-level building block (e.g. OA) Still, it's not always clear how to select higher-level BB or how to encapsulate sub-circuits obtained by evolution.

4-bit DAC

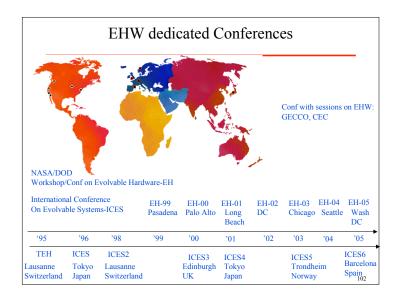

#### **Resources for EHW Engineers**

- Events

- EHW-dedicated conferences

- EHW-related events

- · A guide to published literature and on-line resources

- Journals

- Books

- Selected Articles

- On line resources

- · A guide to tools

- Software

- Hardware

- A guide to people and programs

- Research topics, labs and individual researchers

- Sponsors and funding programs

101

#### EHW-dedicated conferences

#### **Evolvable Hardware Conferences:**

Proceedings of 1999, 2000, 2001, 2002, 2003, 2004 NASA/DoD Conferences (IEEE Computer), (http://computer.org/)

• Forthcoming:

ICES 2005 The 6th International Conference on Evolvable Systems: From Biology to Hardware

Barcelona, Spain, June 2005

Proceedings - Lecture Notes in Computer Science, Springer

2005 NASA/DOD Conference on Evolvable Hardware Washington DC, June 29- July 12005

03

#### **EHW-related Events**

**Evolutionary Computation Conferences:**

2005 IEEE Congress on Evolutionary Computation (CEC 2005)

Sept 2-5, Edinburgh, Scotland

http://www.cec2005.org/

2005 Genetic and Evolutionary Computation COnference (GECCO - 2005 )

June, 25-29 Washington DC

http://www.isgec.org/gecco-2005/

#### **EHW-related Events**

#### **Design Automation Conferences:**

41st Design Automation Conference (DAC) June 7-11, 2004, San Diego CA http://www.dac.com/

International Conference on Computer Aided Design (ICCAD-2004) November 7-11, 2004 S. Jose CA http://www.iccad.com

Design Automation and Test Europe (DATE-2004) February 16-20, 2004 Paris http://www.date-conference.com

105

#### Books

- Thompson, A., "Hardware Evolution: Automatic design of electronic circuits in reconfigurable hardware by artificial evolution", Springer-Verlag, 1998, http://www.cogs.usv.ac.uk/users/adrianth/ade.html

- Zebulum et Al, "Evolutionary Electronics: Automatic Design of Electronic Circuits and Systems by Genetic Algorithms", CRC Press, 2001 http://www.crcpress.com/shopping\_cart/products/product\_detail.asp?sku=0865

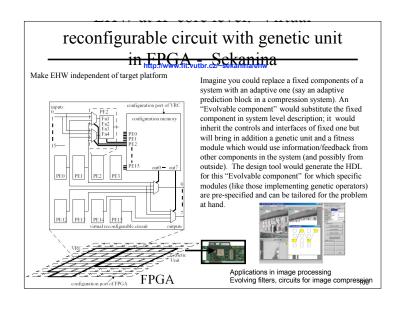

- Sekanina, L., Evolvable Components From Theory to Hardware Implementations", Springer, 2003, <a href="http://www.springer.de/cgi-bin/search\_book.pl?isbn=3-540-40377-9&cookie=done">http://www.springer.de/cgi-bin/search\_book.pl?isbn=3-540-40377-9&cookie=done</a>

- John Koza, "Genetic Programming: On the Programming of Computers by Means of Natural Selection" published by The MIT Press, 1992;

- John Koza, "Genetic Programming II: Automatic Discovery of Reusable Programs" published by The MIT Press, 1994.

- John Koza, "Genetic Programming III: Darwinian Invention and Problem Solving" published by Morgan Kaufmann Publishers, 1999.

- John Koza, "Genetic Programming IV: Routine Human-Competitive Machine Intelligence" (with Martin A. Keane, Matthew J. Streeter, William Mydlowec, Jessen Yu, and Guido Lanza) published by Kluwer Academic Publishers, 2003.

107

#### Journals

- Genetic Programming and Evolvable Machines: http://www.kluweronline.com/issn/1389-2576

- IEEE Transactions on Evolutionary Computation: http://www.ieee-nns.org/

- Evolutionary Computation Journal (MIT Press): http://www.mitpress.mit.edu/EVCO/

- International Journal of SMART ENGINEERING SYSTEM DESIGN Cihan Dagli (Ed), http://web.umr.edu/~dagli

Special issues on EHW in following journals:

- Soft Computing Journal, Special Issue on Evolvable Hardware Adrian Stoica (Ed) <a href="http://www.springer.de">http://www.springer.de</a>

- IEE Proceedings Computer-Digital Techniques

Special Issue on Evolvable Hardware, Andy Tyrrell (Ed)

http://www.iee.org/Publish/Journals/ProfJourn/Proc/CDT/evolvable\_hardware.pdf

106

#### **Books**

- Goldberg, D., "Genetic Algorithms in Search, Optimization and Machine Learning", Addison-Wesley Publishing Company, Inc., Reading, Massachusetts, 1989.

- Holland, J., "Adaptation in Natural and Artificial Systems", University of Michingan Press, Ann Arbor, EUA, 1975.

- Higuchi, T., "Evolvable Hardware and its Applications", chapter in "Computational Intelligence The Expert Speak" by Fogel and Robinson, IEEE Press. 2003.

- Miller, J. F., Thomson, P., and Fogarty, T., "Designing Electronic Circuits

Using Evolutionary Algorithms. Arithmetic Circuits: A Case Study", chapter 6

in Genetic Algorithms Recent Advancements and Industrial Applications.

Editors: D. Quagliarella, J. Periaux, C. Poloni and G. Winter, Wiley, 1997.

#### Selected articles

- Explorations in Design Space: Unconventional Electronics Design Through Artificial Evolution

Thompson, A., Layzell, P., Zebulum, R.S., published at: IEEE Transactions on Evolutionary Computation, Special Issue in "Evolvable Hardware", Moshe Sipper (Ed.), pp.167-196, V.3, N.3, September, 1999.

What's AI done for me lately? Genetic programming's human-competitive results Koza, J.R.; Keane, M.A.; Streeter, M.J.; Intelligent Systems, IEEE [see also IEEE Expert], Volume: 18 Issue: 3, May-June 2003 Page(s): 25-31

A circuit representation technique for automated circuit design Lohn, J.D.; Colombano, S.P.; Evolutionary Computation, IEEE Transactions on , Volume: 3 Issue: 3 , Sept. 1999 Page(s): 205 - 219

Embedded reconfigurable array targeting motion estimation applications

Khawam, S.; Arslan, T.; Westall, F.;

Circuits and Systems, 2003. ISCAS '03. Proceedings of the 2003 International Symposium on , Volume: 2 , May 25-28, 2003

Pages; 780-76 Systems, 2003.

Reconfigurable VLSI Architectures for Evolvable Hardware: from Experimental Field Programmable Transistor Arrays to Evolution-Oriented Chips

Adrian Stoica, Ricardo Zebulum, Didier Keymeulen, Raoul Tawel, Taher Daud, and Anil Thakoor.. IEEE Trans. on VLSI, IEEE Press , Volume 9, Number 1, ISSN 1063-8210, pp. 227-232, Feb. 2001.

- An Overview of Evolutionary Algorithms in Multiobjective Optimization

- Fonseca, C. M, Fleming P. J., Evolutionary Computation, MIT Press, Vol. 3, No.1, pp.1-16, 1995.

Digital Filter Design Using Multiple Pareto Fronts

Thorsten Schnier, Xin Yao, Pin Liu, 2001 NASA/DoD Workshop on Evolvable Hardware, pp.136-145.

109

#### Selected articles

- HW implementations of Evolutionary Processors

- · An FPGA-Based Genetic Algorithm Machine

Shackleford B., Carter D., Snider G, Okushi E., Yasuda M., Koizumi H., Seo K., Iwamoto T., Yasuura H. FPGA 2000, Eighth ACM International Symposium on Field-Programmable Gate Arrays, Feb. 10-11, 2000.

An Evolvable Hardware Platform based on DSP and FPTA

Ferguson, M.I., Stoica A., Zebulum R., Keymeulen D. and Duong, V. Proceedings of the Genetic and Evolutionary Computation Conference, July 9-3, 2002 New York, NY;

- Evolution on FPTAs

- Evolving Circuits in Seconds: Experiments with a Stand-Alone Board Level Evolvable System Stoica, A., Zebulum, R. S., M.I. Ferguson, Keymeulen, D., Duong, V., 2002 NASA/DoD Conference on Evolvable Hardware, Alexandria Virginia, USA, 2002, pp. 67-74 IEEE Computer Society, ISBN 0-7695-1718-8

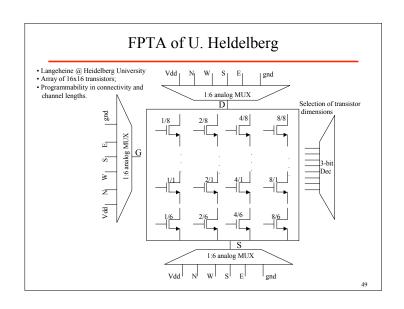

- Intrinsic Evolution of Quasi DC Solutions for Transistor Level Analog Electronic Circuits Using CMOS

Langeheine, J., Meier, K., Schemmel, J., Proceedings of the 2002 NASA/DoD Conference on Evolvable Hardware, pp.75-84, IEEE Computer Press, July, 2002.

- · Evolution of antennas (design)

- Evolutionary Design of an X-Band Antenna for NASA's Space Technology 5 Mission

- J. Lohn, D. Linden, G. Hornby, W. Kraus, A. Rodríguez-Arroyo, and S. Seufert, 2003 NASA/DoD Conference on Evolvable Hardware, pp. 155-163, IEEE Computer

- Fitness Estimations for Evolutionary Antenna Design

- L. Zinchenko and S. Sorokin, 2003 NASA/DoD Conference on Evolvable Hardware, pp. 164-176, IEEE

- Evolving Wire Antennas Using Genetic Algorithms: A Review

Derek S. Linden, Edward E. Altshuler, 1st NASA/DoD Workshop on Evolvable Hardware, pp.225.232, 1999,

Selected articles

- · Evolution on FPAAs

- Analog Circuits Evolution in Extrinsic and Intrinsic Modes

Zebulum, R.S., Pacheco, M.A., Vellasco, M., in Proceedings of the Second International Conference on Evolvable Systems: From Biology to Hardware (ICES98), Lausanne, Switzerland, 1998. M.Sipper, D.Mange e A. Pérez-Uribe (editors), vol. 1478, pp. 154-165, LNCS, Springer-Verlag, 1998.

Behaviour of a building block for intrinsic evolution of analogue signal shaping and filtering circuits Flockton, S.J.: Sheehan, k

Flowards, 3-3, incental, 3-3, incental, 3-3, Evolvable Hardware, 2000. Proceedings. The Second NASA/DoD Workshop on , 13-15 July 2000 Page(s): 117-123

- Evolution of FPGAs

- Silicon Evolution

Thompson, A., in Proceedings of Genetic Programming 1996 (GP96), J.R. Koza et. al. (editors), pp. 444-452, MIT

Evolving Stable Circuits on Mainstream FPGA Devices

Delon Levi, Steven A. Guccione:, 1st NASA/DoD Workshop on Evolvable Hardware, pp.12.17, 1999.

- Fault Tolerance

- Evolutionary design and adaptation of digital filters within an embedded fault tolerant hardware platform Hounsell, B.L., Arslan, T.; Evolvable Hardware, 2001. Proceedings. The Third NASA/DoD Workshop on , 12-14 July 2001

- Fault-Tolerant Evolvable Hardware using Field Programmable Transistor Arrays.

D. Keymeulen, A. Stoica, R. Zebulum, Raoul Tawel, Taher Daud, Anil Thakoor. In IEEE Transactions on Reliability, Special Issue on Fault-Tolerant VLSI Systems, vol. 49, No. 3, 2000 September, pp. 305-316, IEEE

#### Selected articles

- · Evolution on physical antennas

- Optimizing Signal Strength In-Situ Using an Evolvable Antenna System Derek S. Linden , 2002 NASA/DoD Conference on Evolvable Hardware (EH'02) pp. 147-151, 2002, IEEE

- · System On a Chip

- An evolutionary power management algorithm for SoC based EHW systems Lirong Tian; Arslan, T.;

Evolvable Hardware, 2003. Proceedings. NASA/DoD Conference on , July 9-11, 2003

Multi-objective design strategy for high-level low power design of DSP systems

Bright, M.S., Arslan, T.;

Circuits and Systems, 1999. ISCAS '99. Proceedings of the 1999 IEEE International Symposium on , Volume:

1, 30 May-2 June 1999

Page(s): 50 -83 vol.1

· Towards evolvable IP cores for FPGAs

Evolvable Hardware, 2003. Proceedings. NASA/DoD Conference on , July 9-11, 2003 Page(s): 145 -154

- · Parallel EHW

- An EHW architecture for real-time GPS attitude determination based on parallel genetic algorithm Jiangning Xu; Arslan, T.; Qing Wang; Dejun Wan; Evolvable Hardware, 2002. Proceedings. NASA/DoD Conference on , 15-18 July 2002 Page(s): 133-141

#### Selected articles

#### Applications

Real-world applications of analog and digital evolvable hardware

Real-worth applications of nanage and urginal evolvation and water Higuchi, T.; Iwata, M.; Keymeulen, D.; Sakanashi, H.; Murakawa, M.; Kajitani, I.; Takahashi, E.; Toda, K.; Salami, N.; Kajitana, N.; Otsu, N.; Evolutionary Computation, IEEE Transactions on , Volume: 3 Issue: 3 , Sept. 1999

Page(s): 220-235

An evolvable hardware chip for prosthetic hand controller Kajitani, I.; Murakawa, M.; Nishikawa, D.; Yokoi, H.; Kajihara, N.; Iwata, M.; Keymeulen, D.; Sakanashi, H.; Higuchi, T.;

rngucm, 1.; Microelectronics for Neural, Fuzzy and Bio-Inspired Systems, 1999. MicroNeuro '99. Proceedings of the Seventh International Conference on , 7-9 April 1999 Page(s): 179 -186

#### · Low Power design

Synthesis of low-power DSP systems using a genetic algorithm Bright, M.S.; Arslan, T.; Evolutionary, Computation, IEEE Transactions on , Volume: 5 Issue: 1 , Feb 2001 Page(s): 27 -40

· Evolutionary Algorithms

From an individual to a population..." Jun He; Xin Yao. Evolutionary Computation, IEEE Transactions, Volume: 6 Issue: 5, Oct 2002 Page(s): 495-511

113

#### Guide to Software Tools

- Free Evolutionary SW

- (evonet.dcs.napier.ac.uk)

- Free Spice

- Ngspice (<u>sourceforge.net/projects/ngspice</u>)

- Other (<u>www.repairfaq.org/ELE/F\_Free\_Spice2.html</u>)

- · Simulators, GUI

- ModelSim (<u>www.model.com</u>)

- GUI toolkits free/commercial (<a href="http://www.atai.org/guitool">http://www.atai.org/guitool</a>)

- C/C++

- GCC (gcc.gnu.org)

- Rational Rose (OO/UML) (<u>www.rational.com</u>)

- NI

- National Instruments (www.ni.com) LabView

115

#### On-line resources

#### EvoNet Tutorials:

ac.uk/evoweb/resources/flying\_circus/tutorials/index.html

Good repository of GA links: http://www.aic.nrl.navv.mil/galist

EvoWeb, website of EvoNet - the European Network of Excellence in **Evolutionary Computing http:**

Another GA Tutorial http://www.ifs.tuwien.ac.at/~aschatt/info/ga/genetic.html

Evolutionary Multi-Objective Optimization SW <a href="http://www.lania.mx/~ccoello/EMOO/">http://www.lania.mx/~ccoello/EMOO/</a> <a href="http://www.lania.mx/~ccoello/EMOO/">http://www.lania.mx/~cco

Sketchy Tutorial Slides <a href="http://lancet.mit.edu/~mbwall/presentations/IntroToGAs/P001.html">http://lancet.mit.edu/~mbwall/presentations/IntroToGAs/P001.html</a>

Genetic and Evolutionary Algorithms: Principles, Methods and Algorithms

Evolutionary Algorithms for MATLAB (incl. Genetic Algorithms and Genetic Programming) http://www.geatbx.com/links/ea\_matlab.html

An Overview of Evolutionary Algorithms, Genetic Algorithms and Evolutionary Computing http://www.sc.olostate.edu/~genitor/Pubs.html

114

#### Guide to Hardware Tools

- · FPGA development kits

- Xilinx (www.xilinx.com) ISE

- Altera (<u>www.altera.com</u>) MAX+PLUS<sup>®</sup> II

- · FPAA development kits

- · Multi-objective synthesis of VLSI Signal and Image Processing Cores

- www.see.ed.ac.uk/~SLIg

- · SoC development kits

- ARM Integrator Solutions,

- www.arm.com/devtools

- · SoC development kits

- Cadence (www.cadence.com)

- Mentor Graphics (www.mentor.com)

- Data acquisition boards

- National Instruments (<u>www.ni.com</u>) LabView

- Microstar Laboratories (www.mstarlabs.com) DAP Tools

- Microcontrollers, DSP, etc..

- Keil Software (www.keil.com) DK51

- Texas Instruments (www.ti.com) Code Composer

## Sponsors and Funding Programs

- Previous sponsors

NASA JPL/CISM

DARPA Adaptive Computing

#### • Current

- AFRL NASA JPL

- NASA AMES solicitation in Intelligent Systems at http://www2.eps.gov/spg/NASA/ARC/OPDC20220/NRA2-38169/listing.html

The National Science Foundation under Career Award IIS-0238200

- Europe

European Fame work VI

- Integrated Projects

Networks of excellence

- Eureka

- MEDA+

- Engineering and Physical Sciences Research Council

Responsive Mode

Novel Computational paradigms

Department of Trade and Industry