## Large-scale Linear Circuit Simulation with an Inversed Inductance Matrix

Chieki MIZUTA\* Jiro IWAI\* Ken MACHIDA\* Tetsuro KAGE\*\* Hiroo MASUDA\*\*

mizuta@msi.co.jp iwai@msi.co.jp machida@msi.co.jp kage@starc.or.jp masuda@starc.or.jp

\* Mathematical Systems Incorporated 2-4-3 Shinjuku, Shinjuku-ku, Tokyo 160-0022, JAPAN

Tel: +81 3-3358-1701 FAX: +81 3-3358-1701

Abstract - In this paper we show that by using an inversed form of an inductance matrix, the current variables become no more necessary in a transient analysis. Furthermore we have invented a way to remove them even in a steady state analysis while preserving the same sparse matrix topology throughout the both analyses. The removal has brought about a sufficiently effective speed-up and stability of calculation. It opens a way to the accurate numerical verification of large-scale signal

## I. Introduction

integrity as in a power grid of LSI.

The effect of inductance to the signal integrity of power and/or signal lines in LSI are getting more and more important as the size of LSI becomes smaller. In spite of such need, the numerical analysis of a large-scale circuit with a lot of inductive interconnect has been very difficult. The difficulty is brought about mainly by two reasons. One reason is that all the currents flowing through inductors have to be made independent variables in a set of circuit equations according to the conventional method called modified nodal analysis (MNA). These variables inflate the size of circuit matrix and bring about many fill-ins during its LU decomposition. The other reason is that an inductance matrix has high density of non-zero elements when the circuit consists of mutually connected inductance. This also brings about big fill-ins. In order to make a large-scale simulation with inductive circuit

\*\* Semiconductor Technology Academic Center 3-17-2 Shin-yokohama, Kohoku-ku, Yokohama-shi, Kanagawa 222-0033, JAPAN

Tel: +81 45-478-3232 FAX: +81 45-478-3310

interconnect practical, these bottlenecks have to be dissolved.

In this paper we show that by using an inversed form of an inductance matrix, the current variables become no more necessary in a transient analysis. Furthermore we have invented a way to remove them even in a steady state analysis while preserving the same sparse matrix topology throughout the both analyses. The removal brings about sufficiently effective speed-up and stability of calculation.

We also show that from a viewpoint of numerical analysis, off-diagonal elements of the inversed form of an inductance matrix can be removed easily while preserving the sufficient accuracy in simulation, although it is not the case with the conventional form of an inductance matrix.

# II. Circuit Equations

A relation between currents and voltages of inductive elements are represented as follows.

$$v_{i} = \sum_{j=1}^{N} L_{ij} \frac{dI_{j}}{dt} \quad (i = 1...N)$$

(1.1)

Here we shall call this representation L-formula, where  $L_{ij}$  is an inductance matrix. Meanwhile by using a inversed form  $(K_{ij}) = (L_{ij})^{-1}$  as proposed by H.Ji et al.[1][2], L-formula is converted to the following formula which we shall call K-formula.

$$\frac{dI_i}{dt} = \sum_{i=1}^{N} K_{ij} v_j \tag{1.2}$$

In the both formulae the equations are the same in a steady state analysis as follows.

$$v_i = 0 \quad (i = 1...N)$$

(1.3)

# III. Implementation into a circuit simulator -Removal of current variables-

In L-formula  $I_i$  need be made independent variables in the conventional MNA method. In this case the size of a circuit matrix increases by the number of inductive currents and furthermore the diagonal matrix elements corresponding to the currents are zero in a steady state analysis (1.3). This is one of the reasons that a large-scale circuit with interconnected inductance is difficult to solve. We show here that by using K-formula inductive current variables naturally become unnecessary in a transient analysis as is also shown by Beattie et al.[3] and even in a steady state analysis they can be removed.

#### -Transient analysis

By an implicit numerical time integration as Gear's method the following equation is attained from the differential equation of K-formula (1.2).

$$I_i^{n+1} = \sum_{k=1}^m \alpha_k I_i^{n-k+1} + \alpha_0 h \sum_{j=1}^N K_{ij} v_j^{n+1}$$

(2.1)

Here  $\alpha_k$  are coefficients subject to an integration method, h is a time step, m is a order of integration and superscripts represent digitized time points.

According to this equation, each inductive current

$I_i^{n+1}$  is explicitly defined only by voltages and past currents, which means current variables are not needed. Meanwhile in L-formula (1.1) each current is connected to others, which means the currents have to be made independent variables in order to construct a nodal equation according to the Kirchhoff's current law (KCL).

-Steady state analysis

In steady state analysis both K and L-formula have the same equation set of (1.3). As no current can be defined explicitly from this set, it is most natural that current variables be introduced to construct a circuit equation. But it is necessary for the current variables to be removed in a steady state analysis in order to take advantage of the above-mentioned numerically superior characteristic of K-formula.

-Removal of current variables in a steady state analysis Suppose an inductor exists in a circuit without directly connected to other inductors, then nodal equations at the end-point node i and j are represented by the following equations (2.2) and (2.3) where I is the current through the inductor,  $v_i$  is a voltage at node i, et cetera.

$$a_i v_i + a_j v_j + I + \sum_{k \neq i, j} a_k v_k = c_i$$

(2.2)

$$b_i v_i + b_j v_j - I + \sum_{k \neq i,j} b_k v_k = c_j$$

(2.3)

Add (2.2) to (2.3) and we get an equation with the current I disappeared, that means the old nodal equations (2.2) and (2.3) are replaced by the new ones (2.4) and (2.5) as follows.

$$(a_i + b_i)v_i + (a_j + b_j)v_j + \sum_{k \neq i,j} (a_k + b_k)v_k = c_i + c_j$$

(2.4)

$$v_i - v_j = 0 \tag{2.5}$$

In actual cases where inductors are not necessarily isolated, a little more complicate technique is needed as shown below.

-Removal algorithm of current variables in steady state analysis-

Prepare work-table Lnode[N] and a counter ln. Initialize the both. (N is the number of nodes.)

#### Foreach L:

Lnode[i] += 1, Lnode[j] += 1, ln +=2 (i, j are end-point nodes of L.)

Construct a circuit matrix without L.

#### While ln>0:

#### Foreach L(i,j):

If Lnode[i]=1 then add i-node equation to j-node eq. and replace i-node eq. by  $v_i\text{-}v_j\text{=}0.$

Let Lnode[i]=0, Lnode[j]=1 and ln=2.

Else if Lnode[j]=1 then replace i and j and do the same as above.

Else do nothing.

This method corresponds to short-circuiting each inductor sequentially, beginning with an isolated terminal node of a certain inductor. Note that the process of this algorithm always stops successfully without leaving zero diagonal entries attributing to inductors in the circuit matrix. It is proved recursively as follows.

## -proof

- 1) If a circuit includes only one inductor with terminal nodes i and j, nodal equations at i and j turn to be ones as (2.5) and (2.4) that means diagonal entries are 1 and  $a_j + b_j$ .

- 2) In any circuit, an inductor, if there are any, not connected to other inductors at one terminal node is always found. If such an inductor is not found, the circuit include an inductor loop. Let the node found be i and the other node of the inductor be j. Let a nodal equation at node i be equation (2.5) and node j be equation (2.6) below, a slight modification of (2.4), where otherL is other inductors connected to j, if any.

$$(a_{i} + b_{i})v_{i} + (a_{j} + b_{j})v_{j} + \sum_{k \neq i, j} (a_{k} + b_{k})v_{k}$$

$$+ \sum_{j \neq i, l} I_{otherL} = c_{i} + c_{j}$$

(2.6)

This is interpreted that the node i is eliminated as well as the inductor by short-circuiting i and j. Remove node i and the inductor from the further consideration. Thus a new circuit with one inductor less is created. Here the value of (i,i) entry of the matrix becomes 1.

3) Proceed the process No. 2 until getting to the situation of the process No. 1.

# IV. Characteristics of circuit equations derived from L-formula and K-formula

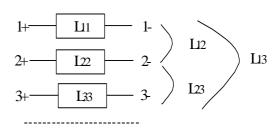

Suppose N wires are interconnected by self and mutual inductance as in the figure below, we get an set of equations of voltages and currents as represented in (3.1).

$$V_{i+} - V_{i-} = \sum_{i=1}^{N} L_{ij} \frac{dI_i}{dt} \quad (i = 1...N)$$

(3.1)

This is shown as a matrix form below, where N is set to be 3 for the convenience of easiness of representation.

$$\begin{bmatrix} 1 & 0 & 0 \\ -1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & -1 & 0 \\ 0 & 0 & 1 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{1+} \\ V_{1-} \\ V_{2+} \\ V_{2-} \\ V_{3+} \\ V_{3-} \\ V_{3+} \\ V_{3-} \\ V_{3+} \\ V_{3-} \\ V_{3$$

Here  $D = \frac{d}{dt}$ . By applying a numerical integration as

Gear's method, D is converted to  $\frac{1}{\alpha_0 h}$  and 0 of the

right hand side corresponding to each  $I_i$  is replaced

by

$$-\frac{1}{\alpha_0 h} \sum_{j=1}^3 L_{ij} \sum_{k=1}^m \alpha_k I_j^{n-k+1}$$

.

Meanwhile, by K-formula we get equations (3.3) and its matrix form (3.4).

$$K_{11}(V_{1+} - V_{1-}) + K_{12}(V_{2+} - V_{2-}) + K_{13}(V_{3+} - V_{3-}) = \frac{dI_1}{dt}$$

$$K_{21}(V_{1+} - V_{1-}) + K_{22}(V_{2+} - V_{2-}) + K_{23}(V_{3+} - V_{3-}) = \frac{dI_2}{dt}$$

$$K_{31}(V_{1+} - V_{1-}) + K_{32}(V_{2+} - V_{2-}) + K_{33}(V_{3+} - V_{3-}) = \frac{dI_3}{dt}$$

$$(3.3)$$

$$k_{ij} = K_{ij} / K_{ii} \quad (i \neq j), \quad k_{ii} = 1/K_{ii}$$

(3.4)

Here current variables are used in K-formula for the convenience of comparison between the two formulae without losing the validity of the discussion in this section.

Suppose there are inductors in a circuit not connected directly to one another but interconnected by mutual inductance, which is usual in parasitic interconnection, the number of non zero elements in a circuit matrix in L-formula is represented as:

$$N_{nonzero}^{(L-formula)} = 2N + N^2 + 2N = N^2 + 4N$$

while in K-formula

$$N_{nonzero}^{(K-formula)} = N \times 2N + N + 2N = 2N^2 + 3N$$

(Here N is the number of inductors.)

This shows that the number of non-zero elements in K-formula is about twice as many as that in L-formula, which means that in order to make the non-zero matrix element number in K-formula even to that in L-formula, about 50% of elements have to be removed.

Fortunately  $K_{ij}$  (and also  $K_{ji}$ ) can be removed without much effecting numerical errors because off-diagonal element  $k_{ij} = K_{ij} / K_{ii}$  is much smaller

compared to its diagonal element

$$-\frac{1}{\alpha_0 h K_{ii}}$$

.

Meanwhile  $L_{ij}$  cannot be removed without effecting

serious numerical error because it is the same as dropping out a big-value matrix element of  $-\frac{L_{ij}}{\alpha_0 h}$ .

# V. Numerical experiment

-Test conditions

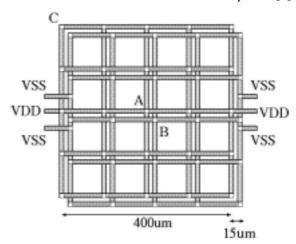

Circuits assumed to be a power gird of LSI as shown in Figure 1 are used here, where VDD=1.2V, VSS=0V and a current source is inserted between node A and node B. The shape of the current is triangular with the width of 0.2 ns and the maximum value of 0.58A. The voltage is monitored at node C. Figure 1 shows an image of the grids, not the actual ones used here. We prepare two sizes, a middle size and a small size. The middle size gird consists of 1052 resisters, 2452 capacitors and 978 inductors. The small size one consists of 144 resisters, 224 capacitors and 90 inductors. The number of mutual inductance is different in each example, which is shown in each table if necessary. The values of resisters, capacitors and inductors are gained by our parasitic interconnect extraction tool called PowerSpective[4].

Fig. 1. Image of a power grid

-Test result

Table 1.1 and 1.2 shows an effect of the removal of current variables to the number of fill-in elements after LU decomposition.

Table 2.1 shows the numbers of non-zero elements of circuit matrices constructed in L-formula and in

#### K-formula.

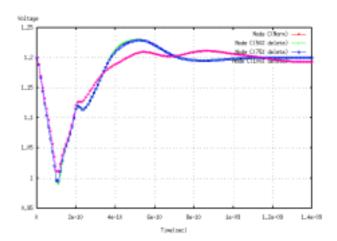

Figure 2 and table 2.2 shows the effect of the calculation accuracy according to the reduction of K elements in K-formula.

Table 1.1 Effect of the removal of current variables (in a middle size case)

| Current   | Matrix | Non0s   | Fill-ins | time (s) |

|-----------|--------|---------|----------|----------|

| Variables | size   |         |          |          |

| removed   | 2,038  | 512,914 | 764,950  | 237      |

| used      | 3,016  | 264,663 | 2870,363 | 1,063    |

Here Non0s stands for no. of non-zero elements before the ordering, Fill-ins for no. of fill-ins after the ordering and time(s) for the cpu time consumed for the total simulation. The number of mutual inductive interconnect is 126,890. Minimum degree algorithm is used as an ordering method.

Table 1.2 Effect of the removal of current variables (in a small size case)

| Current   | Matrix | Non0s  | Fill-ins | Calculation |

|-----------|--------|--------|----------|-------------|

| Variables | size   |        |          | time (s)    |

| removed   | 210    | 11,784 | 6,518    | 2.54        |

| used      | 300    | 6,637  | 30,725   | 2.74        |

Here the number of mutual inductive interconnect is 3,874.

Table 2.1 The numbers of non-zero elements in circuits matrices constructed in K-formula and L-formula respectively

|           | Middle size | Small size |  |  |  |

|-----------|-------------|------------|--|--|--|

| K-formula | 3,826,466   | 32,566     |  |  |  |

| L-formula | 1,921,895   | 17,069     |  |  |  |

Densely connected mutual inductance is assumed. Numerical calculation is not performed in this case because of its difficulty especially in L-formula.

Fig. 2. Effect of the calculation accuracy by the reduction of K element of K-formula

Table 2.2 Effect of the calculation accuracy by the reduction of K element of K-formula

| Degree of | Peak voltage | Accuracy   | No. of    |

|-----------|--------------|------------|-----------|

| Removal   |              | comparison | mutual Ks |

| Norm      | 1.0105       | 100.0%     | 126890    |

| 50%       | 0.9973       | 98.9%      | 63446     |

| 75%       | 0.9951       | 98.5%      | 31722     |

| 100%      | 0.9906       | 98.0%      | 0         |

# -discussion

The most time consuming part of calculation in linear circuit simulation is LU decomposition. The most effective way to speed up its calculation is to reduce the number of its fill-ins. To minimize fill-ins, so-called static ordering is most desired, where only a topological connection in a matrix is considered, unrelated to its element values, although zero pivoting has to be avoided during LU decomposition. In a conventional method to use current variables it is very difficult to avoid this in a steady state analysis especially when a circuit has a large number of inductors. In this paper we showed a newly invented way to avoid this difficulty by removing current variables. We checked its effect in our linear circuit simulator that the number of fill-ins is greatly reduced, the stability of calculation is much improved and the effect increased according to the size of a circuit. The advantage of this method is that the

same circuit matrix topology can be used both in a steady state analysis and a transient analysis.

Meanwhile we learned that non-zero elements in a circuit matrix doubles in K-formula to that in L-formula but the calculation accuracy does not degrade so much by the removal of K elements in K-formula even when removed by 50% or 75%.

## VI. Conclusions

Large-scale circuit simulation with parasitic inductors has been very difficult because of current variables introduced in a circuit equation according to the MNA method used in conventional circuit simulators as SPICE. We invented the way to remove these variables using an inversed inductance matrix. We implemented the method in our linear circuit simulator LiCRSIM and learned that it has sufficient effect to speed and stability of the simulation.

### VII. Acknowledgement

The authors greatly appreciate advices from members of STARC KCR Sub-working-group, who are Mr. Shinji Ito of Hitachi ULSI Systems, Mr. Nobuto Ono of SII EDA Techonology, Mr. Toshiki Kanamoto and Mr. Takashi Sato of RENESAS Technology, Mr. Atsushi Kurokawa and Mr. Fumihiro Minami of STARC and Mr. Kotaro Hachiya of NEC Electronics. I also appreciate Mr. Tsutomu Kurihara of Mathematical Systems Inc., who offered us interesting test results.

#### VIII. References

[1]H. Ji, A. Devgan, and W. Dai, "Ksim:A Stable and Efficient RKC Simulator for Capturing On-Chip Inductance Effect", UCSC Technique Report, UCSC-CRL-00-10, Apr. 2000

[2]A. Devgan, H. Ji and W. Dai, "How to efficiently capture on-chip inductance effect: Introducing a new circuit element K" in Proc. IEEE International Conference on Computer Aided Design, pp. 150-155,

Nov. 2000

[3]M. Beattie and L. Pileggi, "Modeling Magnetic Coupling for On-chip Interconnect", Proc. 38<sup>th</sup> Design Automation Conference, June 2001

[4]J. Iwai, K. Machida, H. Kayama, C. Mizuta, K. Tokumasu, H. Masuda "Parasitic Element Extraction and Noise Analysis in LSI Power Grids", DA Symposium 2002, July 2002 (in the Japanese language)