# Capturing Crosstalk-Induced Waveform for Accurate Static Timing Analysis

Masanori Hashimoto Dept. Communications & Computer Engineering Kyoto University

hasimoto@i.kyoto-u.ac.jp

Yuji Yamada

Dept. Communications &

Computer Engineering

Kyoto University

yuji@vlsi.kuee.kyotou.ac.jp Hidetoshi Onodera

Dept. Communications &

Computer Engineering

Kyoto University

onodera@i.kyoto-u.ac.jp

# **ABSTRACT**

We propose a method to capture crosstalk-induced noisy waveform for crosstalk-aware static timing analysis. The effects of capacitive coupling noise on timing are conventionally measured as delay variation. On the other hand, the propose method derives an equivalent waveform to a crosstalk-induced noisy waveform. The crosstalk effects on timing are all included in the equivalent waveform. With the derived equivalent waveform, we can perform static timing analysis with consideration of dynamic delay variation due to crosstalk noise. The equivalent waveform is derived by our improved least square fitting with weighting coefficient. Our method can naturally consider the slew variation due to crosstalk noise as well as the delay variation. We experimentally verify that our method can estimate the delay variation at the output of the receiver gate accurately. The strength is that the proposed method requires no additional library characterization and is easy to be integrated into usual static timing analysis methods.

# **Categories and Subject Descriptors**

B.7.2 [Integrated Circuits]: Design Aids.; B.8.2 [Performance and Reliability]: Performance Analysis and Design Aids.

#### **General Terms**

Algorithms, Performance, Design.

# **Keywords**

static timing analysis, delay calculation, crosstalk noise, capacitive coupling noise, slope propagation.

# 1. INTRODUCTION

Crosstalk noise has become a critical problem in DSM LSI design, especially crosstalk-induced delay variation is significant and hence circuit designers have to perform crosstalk-aware timing analysis. For this purpose, conventional methods [1–6] estimate the

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

ISPD'03, April 6–9, 2003, Monterey, California, USA. Copyright 2003 ACM 1-58113-650-1/03/0004 ...\$5.00.

amount of delay variation. Reference [1] derives so-called "delay change curve" that expresses the relationship between delay variation and relative transition timing between aggressor and victim. The authors apply the relationship to the relative window method proposed in Ref. [2]. References [3-5] discuss how to estimate the worst-case delay. The methods [1, 3, 4, 6] evaluate the delay variation at the end of the coupled interconnects. However the 50% crossing time of crosstalk-induced noisy waveform at the end of the coupled interconnect is meaningless, because the noisy waveform itself affects the propagation delay of the next receiver gate [5]. We therefore have to evaluate crosstalk noise effects including the receiver gate. Thus the methods [1,3,4,6] can not evaluate true delay variation effects due to crosstalk noise. References [2, 5] evaluate the delay variation at the output of the receiver gate. However Ref. [2] basically evaluates delay variation by circuit simulation and hence it is not suitable for large circuits. Reference [5] proposes an efficient method based on lookup tables. The weakness of this method is that additional cell characterization and library structure modification are required.

In static timing analysis, waveforms are propagated throughout a circuit from primary inputs to primary outputs. Usually, gate propagation delay and output transition time(slew) are characterized in advance assuming some input waveforms expressed as one parameter e.g. slew. The input waveform is usually represented as linear function and/or exponential function. However crosstalk-induced waveform is much different from the assumed input waveforms. Therefore the derivation of the waveform that is propagated to the next gate is one of the large error sources in timing analysis.

In this paper, we propose an equivalent waveform approach to capture crosstalk-induced delay variation. Our method pushes all crosstalk effects into the equivalent waveform, i.e. delay variation and slew degradation are expressed in the shape of the equivalent waveform. The proposed method aims not to fit the waveform at the end of the coupled interconnects but to match the output waveform of the receiver gate. We devise an improved least-square fitting with weighting coefficient in order to consider the output behavior of the receiver gate. The propose method is simple and does not need any additional library characterization, and hence our method is easy to be implemented in usual static timing analysis methods.

The rest of this paper is organized as follows. Section 2 discusses the previous approaches and their problems are explained with some experiments. Section 3 shows the proposed approach of deriving equivalent waveform to consider crosstalk effects on timing. Section 4 demonstrates some experimental results, and the discussion of this paper is concluded in Section 5.

# 2. PREVIOUS APPROACHES

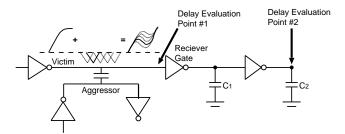

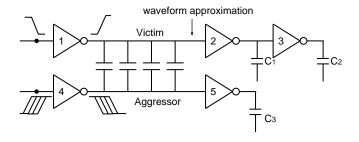

This section discusses the previous approaches that evaluate the amount of delay variation due to crosstalk noise, and explains the problems of the previous approaches using some experiments. Figure 1 shows a pair of coupled interconnects. The transition waveform at the victim is affected by the transition at the aggressor, and it changes according to the transition timing of the aggressor. Most of conventional methods [1, 3, 4, 6] evaluate the timing of crossing  $0.5V_{\rm dd}$  at the point of #1 in Figure 1, and define the amount of delay variation as the difference of  $0.5V_{\rm dd}$  crossing timing with and without crosstalk noise. Reference [1] derives the relationship between delay variation and transition timing, and utilizes it for crosstalk-aware timing analysis. However, in static timing analysis, the transition time(slew) as well as the arrival time is propagated to the next receiver gate. The conventional methods focus on the estimation of the arrival time and think little of the waveform shape. Usually the delay characteristics of gates are characterized assuming normal input waveform like exponential and/or ramp function without noise. Although we must obtain the slew from the crosstalk-induced waveform and propagate it to the receiver gate, its derivation is not carefully discussed so far.

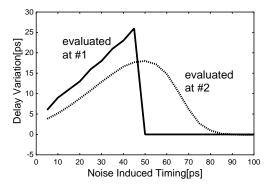

We here demonstrate the problem of the conventional methods [1,3,4,6]. We evaluate the amount of delay variation at both points of #1 and #2 in Figure 1. The delay variation evaluated at #2 can be regarded as the true delay variation caused by crosstalk noise, because the evaluated variation includes the variation due to noisy waveform and the noisy waveform is almost reshaped to normal waveform by two-gate propagation. On the other hand, the conventional method estimates the delay variation at #1, and commonly assumes that crosstalk noise does not change the slew of the input waveform. Therefore the crosstalk-induced delay variations at #1 and #2 are estimated as the same value by the conventional method. We here show the difference of the delay variations at #1 and #2.

The crosstalk-induced delay variations are evaluated by circuit simulation. The waveform at #1 is generated as the sum of the following two waveforms; a normal transition waveform i.e. a waveform without crosstalk noise, and the triangle waveform that corresponds to crosstalk noise. We change the timing of inducing noise waveform. We use the transistor parameters of a  $0.13\mu m$  CMOS technology. The drivers are standard-size inverters. The supply voltage is 1.2V. As for a noise waveform, we suppose that the peak noise voltage is 0.3V and the rise/fall transition times of noise waveform are 30ps. In this analysis, we use the transition waveform model proposed in Ref. [7] as a normal transition waveform. In this model, the signal changes linearly from 0 to  $0.6V_{\rm dd}$ . After that, the waveform is expressed as an exponential function.

Figure 1: Circuit used for Evaluating Crosstalk-Induced Delay Variation.

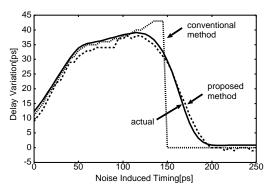

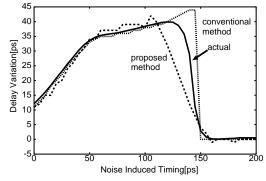

Figure 2: Crosstalk-Induced Delay Variation( $T_{12}$ =20ps,  $C_1, C_2$ =10fF).

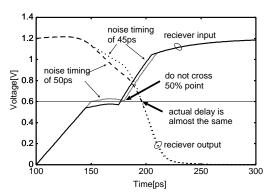

Figure 3: Waveforms of Noise Induced Timing of 45ps and  $50ps(T_{12}=20ps, C_1, C_2=10fF)$ .

The parameter of this model is only one parameter of  $T_{12}$ .

$$f_{\text{rise}}(t) = \begin{cases} 0 & 0 \le t \le t_{\text{s}}, \\ V_{\text{dd}} \frac{0.2(t - t_{\text{s}})}{T_{12}} & t_{\text{s}} \le t \le t_{\text{s}} + 3T_{12}, \\ V_{\text{dd}} (1 - 0.4e^{-\frac{t - 3T_{12} - t_{\text{s}}}{2T_{12}}}) & t_{\text{s}} + 3T_{12} \le t. \end{cases}$$

(1)

Figure 2 shows the crosstalk-induced delay variation evaluated by circuit simulation. The vertical axis represents the delay variation due to crosstalk noise, and the positive value means delay increase. The horizontal axis corresponds to the timing of aggressor transition. The curve evaluated at #1 changes drastically between 45ps and 50ps of the noise induced timing. Figure 3 shows the waveforms in the cases that noise is injected at 45ps and 50ps. Though the difference is only whether the waveform crosses  $0.5V_{\rm dd}$ three times or just one time, the delay variation estimated at #1 is much different. This unnatural behavior comes from the definition of the delay time; the delay time is defined as the time difference of crossing  $0.5V_{\rm dd}$  points. However the true delay variation caused by crosstalk noise, which corresponds to the curve at #2, changes smoothly. In Figure 3, we verify that the output waveform of the receiver gate is almost the same. In this way, the most of conventional methods can not estimate the true delay variation.

In order to solve this problem, Refs. [2, 5] estimate the delay variation at the output of the receiver gate. Reference [2] derives the relationship between delay variation and transition timing by circuit simulation. Each pair of coupled interconnects has different size of drivers, coupling length, coupling position, the output load of the receiver gate, and so on, and hence circuit simulation must be executed for each pair of coupled interconnects. This compu-

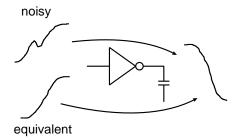

Figure 4: Proposed Concept of Equivalent Waveform.

tational cost is very expensive and static timing analysis for large circuits is infeasible. Reference [5] proposes a lookup table approach to estimate delay variation at the output of the receiver gate. The authors examine the tendency of crosstalk-induced delay variation and they build compact lookup tables with a smart parameter selection. However even though the size of lookup table is not so large, the additional characterization procedure is necessary and the modification of library structure is required. Moreover this method considers only delay variation and does not take the output slew variation of the receiver gate into consideration. Next section discusses how the proposed method overcomes the problems.

# 3. PROPOSED APPROACH OF DERIVING EQUIVALENT WAVEFORM

The conventional methods estimate the delay variation at the end of the victim interconnect or at the output of the receiver gate, and they add/subtract the variation from the usual arrival time without crosstalk noise. On the other hand, our approach does not derive the delay variation at any points. The proposed method derives the equivalent waveform such that the output waveforms of the receiver gate match in both cases that the equivalent and noisy waveforms are given to the receiver input. This concept is shown in Figure 4. The proposed method does not cling to adjust  $0.5V_{\rm dd}$ crossing timing. We derive the equivalent waveform by adjusting both arrival time and slew, for example  $t_s$  and  $T_{12}$  in Eq. (1). In this approach, except the derivation of equivalent waveform, the fundamental techniques of gate and interconnect delay calculation are the same with those of the conventional static timing analysis without crosstalk noise. Any additional characterization and circuit simulation are not required at all. So far, many estimation methods of crosstalk noise waveform have been proposed [6, 8, 9]. With those estimation methods of crosstalk noise waveform, we can perform crosstalk-aware timing analysis just like the longest and the shortest path delay analysis<sup>1</sup>. Our approach can also take the output slew variation of the receiver gate into account. Here the key technique is deriving the equivalent waveform.

This section discusses how to derive the equivalent waveform of crosstalk-induced noisy waveform. We first discuss two simple methods and examine the reason why they do not work well. Next we explain the improved method that overcomes the drawbacks of the simple methods.

#### 3.1 Naive Methods

We take up the following two simple methods and make the problems of them clear.

**Least-Square Fitting**: We derive the equivalent waveform g(t)

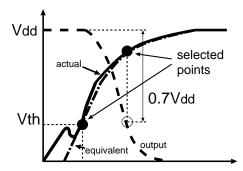

Figure 5: Derivation from Two Waveform Points.

using the technique of least-square fitting. The objective function to minimize is

$$\int_{t_1}^{t_2} \{f(t) - g(t)\}^2 dt,\tag{2}$$

where f(t) is the crosstalk-induced waveform. Times  $t_1$  and  $t_2$  are decided such that the time region between  $t_1$  and  $t_2$  includes the signal transition of the input waveform completely.

Two Point Passing: We pick up two points of the waveform and calculate the waveform that goes on the two points(Fig. 5). Usually waveform expressions have two unknown parameters, arrival time and slew, and hence we use two points to decide the equivalent waveform deterministically. The important thing here is how to select the two points used for waveform derivation. We decide that the first point is the last point crossing NMOS(output rising)/PMOS(output falling) threshold voltage because the regions below NMOS threshold and above PMOS threshold voltage scarcely affect the output transition. The second point is decided such that the voltage swing of the output transition becomes  $0.7V_{\rm dd}$ . This is because the input waveform in the time region after the output transition almost finishes has only small impact on the output waveform.

# 3.2 Experimental Evaluation

We here evaluate the accuracy of the methods shown in Section 3.1 and discuss why those methods do not work well. The evaluated circuit is shown in Figure 6. We evaluate the delay variation at the output of Gate 3. We change the transition timing of the aggressor driver and generate various crosstalk-induced waveforms. When we use the methods in Section 3.1, we derive the

Figure 6: Circuit used for Experiments in Sections 3 and 4.

<sup>&</sup>lt;sup>1</sup>Rigidly speaking, timing window calculation and aggressor alignment are also required.

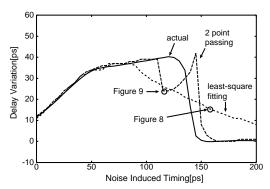

Figure 7: Delay Variation Estimated using Two Point Passing and Least-Square Fitting Methods.

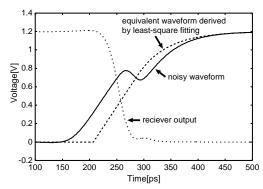

Figure 8: Noisy, Equivalent and Output Waveforms in Least-Square Fitting Method.

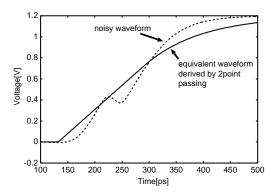

Figure 9: Noisy Waveform and Equivalent Waveform derived by Two Point Passing Method.

**Table 1: Parameters used for Experiments.**

| Cc      | Cg      | R                | Length | $C_1, C_2$ | $C_3$ |

|---------|---------|------------------|--------|------------|-------|

| (fF/µm) | (fF/µm) | $(\Omega/\mu m)$ | (mm)   | (fF)       | (fF)  |

| 0.0575  | 0.0960  | 0.0846           | 1.0    | 1,10,100   | 10    |

equivalent waveform at the input of Gate 2. Then the derived equivalent waveform is given to the receiver input, and we evaluate the 50% crossing time at the output of Gate 3. The parameters used for the experiments are listed in Table 1. We suppose intermediate interconnects in a  $0.13\mu\mathrm{m}$  technology. Parameter Cc is the coupling capacitance between two adjacent interconnects, and Cg is the interconnect capacitance to the ground. Resistance R is the interconnect resistance. Parameters  $C_1, C_2$  and  $C_3$  are the capacitance shown in Figure 6. The coupled interconnect is expressed as 10 segments of CRC  $\pi$  circuit with coupling capacitance. The input waveform given to the aggressor and victim drivers are the waveform expressed as Eq. (1). We assume that the equivalent waveform is express as Eq. (1). We then change  $t_{\rm s}$  and  $t_{\rm s}$  in equivalent waveform calculation.

Figure 7 represents the relationship between the noise induced timing and the amount of delay variation. The curve labeled "actual" represents the circuit simulation result without replacing noisy waveform with equivalent waveform. In this analysis,  $C_1, C_2$ are 1fF and  $T_{12}$  is 40ps. The aggressor and victim drivers are 3xand 4x inverters. As you see, both methods do not work well. We choose the representative points where each method fails. The selected points are drawn in Figure 7. Figure 8 shows the original noisy waveform, the equivalent waveform derived by least-square fitting and the output waveform of the receiver gate. In this case, the output load of the receiver gate is small and the input transition is not so fast. So the output of the receiver gate changes quickly compared with the input transition. When the noise is induced, the output transition almost finishes. However, because least-square method only considers the input waveform and does not take the output transition of the receiver gate into consideration, the equivalent waveform gets close to the all over noisy waveform. Therefore the waveform region that strongly affects the output transition is not paid attention to particularly. Thus in order to estimate the crosstalk-induced delay variation, it is essential to consider output transition of receiver gate. This is also discussed in Reference [5]. Figure 9 shows the original noisy waveform and the equivalent waveform derived by two point passing method. We can not see definitely that this method provides a good equivalent waveform.

# 3.3 Proposed Method

In the previous section, we can see that the consideration of the transition characteristic of the receiver gate is essential for accurate estimation. In order to take the behavior of the next gate into consideration, we devise a modified least-square fitting with weighting coefficient. The objective function to minimize is expressed as

$$\int_{t_1}^{t_2} \left| \frac{\partial v_{\text{out}}}{\partial v_{\text{in}}} \right|_{v_{\text{in}} = f(t)} \left| \left\{ f(t) - g(t) \right\}^2 dt, \tag{3}$$

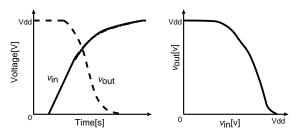

where f(t) is the original noisy waveform and g(t) is the equivalent waveform that we want to obtain. Function  $v_{\rm in}$  is the input waveform of the receiver gate without crosstalk noise, and  $v_{\rm out}$  is the output waveform of the receiver gate without crosstalk noise. Times  $t_1$  and  $t_2$  are decided such that the time region between  $t_1$  and  $t_2$  includes the signal transition of the input waveform completely. Figure 10 represents an example of the weight  $\partial v_{\rm out}/\partial v_{\rm in}$ . The left figure shows the input waveform  $v_{\rm in}$  and the output waveform  $v_{\rm out}$  in time domain. The right figure represents the relation between  $v_{\rm in}$  and  $v_{\rm out}$ . The weight  $\partial v_{\rm out}/\partial v_{\rm in}$  means the slope of the curve in the right figure. This weight value expresses the sensitivity of  $v_{\rm out}$  to  $v_{\rm in}$ . When the absolute weight value is small, the change of  $v_{\rm in}$  scarcely varies the output voltage. Conversely the absolute weight value is large, slight change of  $v_{\rm in}$  affects  $v_{\rm out}$  considerably. Thus, the input waveform in the region where the

Figure 10: Input and Output Waveforms in Time Domain (Left Figure), and Relationship between Gate Input and Output Voltages (Right Figure).

absolute weight value is large dominantly determines the output behavior, and hence we should pay much attention to the region with the large absolute weight value. With this strategy, Eq. (3) is devised. Static timing analysis methods usually have the waveforms of  $v_{\rm in}(t)$  and  $v_{\rm out}(t)$ , though the waveform expression may be different in each method. In this case, the weight value can be calculated easily as follows:

$$\frac{\partial v_{\text{out}}}{\partial v_{\text{in}}} = \frac{\partial v_{\text{out}}}{\partial t} \cdot \frac{\partial t}{\partial v_{\text{in}}} = \frac{\partial v_{\text{out}}}{\partial t} \cdot \frac{1}{\partial v_{\text{in}}/\partial t}.$$

(4)

Therefore the proposed derivation method of the equivalent waveform does not need peculiar information, and the required information is usually stored in static timing analysis tools.

#### 4. EXPERIMENTAL RESULTS

This section demonstrates some experimental results.

#### 4.1 Accuracy Evaluation

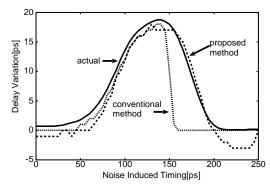

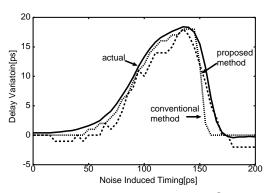

We evaluate the accuracy of the proposed method. Many estimation methods of crosstalk noise waveform have been proposed so far [6, 8, 9]. We assume that the accurate noise waveforms are given by the existent estimation methods. The circuit used for the experiment is the same with Section 3, and it is shown in Figure 6. The victim driver is 8x or 4x inverter. We use 16x inverters as the aggressor driver and receiver. We also vary  $C_1, C_2$ . Figures 11-13 show the relationship between the noise induced timing and the amount of delay variation. The curve labeled "actual" represents the circuit simulation result. The curve of "proposed method" is estimated by the proposed method explained in Section 3.3. The curve of "conventional method" represents the delay variation at the input of Gate 2 in Figure 6. Because the conventional method estimates the delay variation at the input of Gate 2 and does not change the slew. In Figures 11 and 13, "conventional method" does not work well, and the curves change drastically at the noise induced timing of 150ps. This reason is the same with that explained in Section 2. As you see, the proposed method estimates the crosstalk-induced delay variation well. Both the maximum delay variation and its noise-induced timing are derived accurately. In Figure 12, the proposed method also provides the accurate relationship between the delay variation and the noise induced timing. We evaluate the proposed method under other various conditions of aggressor driver, victim driver and  $C_1, C_2$ . In those evaluations, the worst case of the proposed method is shown in Figure 14. Even in the worst case, the maximum error of the proposed method is smaller than that of "conventional method" and the average errors of both the methods are almost the same whereas the noise induced timing that makes the delay variation maximum is somewhat different. From the above results, we can see that the proposed method

Figure 11: Crosstalk-Induced Delay Variation (Gate 1 8x, Gate 2 4x, Gate 3 4x, Gate 4, 5 16x,  $C_1$ ,  $C_2$ =100fF).

Figure 12: Crosstalk-Induced Delay Variation (Gate 1 8x, Gate 2 4x, Gate 3 4x, Gate 4, 5 16x,  $C_1$ ,  $C_2$ =10fF).

Figure 13: Crosstalk-Induced Delay Variation (Gate 1 4x, Gate 2 4x, Gate 3 4x, Gate 4, 5 16x,  $C_1$ ,  $C_2$ =10fF).

Figure 14: Crosstalk-Induced Delay Variation (Gate 1 4x, Gate 2 4x, Gate 3 4x, Gate 4, 5 16x,  $C_1$ ,  $C_2$ =10fF).

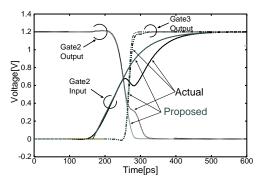

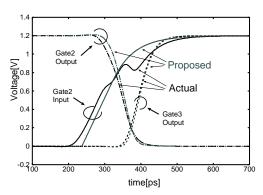

Figure 15: Crosstalk-Induced Waveforms(Gate 1, 2, 3 4x, Gate 4, 5 8x,  $C_1$ ,  $C_2$ =1fF.)

Figure 16: Equivalent Waveform Derivation with Two Aggressors.

estimates the crosstalk-induced delay variation well.

We next examine the crosstalk-induced waveforms. Figure 15 shows the waveforms in the similar situation to Fig. 3. At the input of Gate 2, the waveform goes across  $0.5V_{\rm dd}$  multiple times. The proposed method derives the equivalent waveform that does not follow the final  $0.5V_{\rm dd}$  crossing timing, as we expected. At the outputs of Gate 2 and Gate 3, the proposed method provides the accurate waveforms close to those of circuit simulation results. On the other hand, the conventional methods shift the input waveform to fit the final  $0.5V_{\rm dd}$  crossing timing, and hence the considerable amount of estimation error occurs. In this case, 50ps error would be induced. The proposed method focuses on the important region before the fall transition at Gate 2 finishes. Thus the proposed method overcomes the drawback of the conventional method and the simple least-square fitting discussed in Section 3.1.

We also verify the effectiveness of the proposed method against the interconnect with two aggressors. We add an aggressive net into the circuit shown in Fig. 6, and use it for the experiments. Figure 16 shows a waveform example of the experimental results. As you see, the proposed method works well in the same procedure even when there are multiple aggressors. We verify that our method works well under various conditions.

# 4.2 Discussion on Computation Cost

We here make a brief discussion on the computation cost of the proposed method. At a glance, the proposed method may be thought to require much computation cost, because our method basically performs least-square fitting. We agree that this calculation cost is not small. However the proposed method method does not increase computation time so much in our preliminary experiments. We evaluate the number of iteration required to minimize Eq. (3). In the conditions shown in Figures 11-14, the number of iteration to derive each equivalent waveform is from three to five. The initial equivalent waveform before fitting is the waveform without crosstalk noise. The number of iteration required for fitting is not so large.

We implement the proposed method with a STA tool and roughly evaluate the increase in computational cost. When crosstalk noise is induced, ten to twenty segments are necessary for numerical integration of Eq. (3). If all the waveforms at gate inputs are crosstalk-induced, the increase is about 30%. In this evaluation, the time of file I/O and RC reduction is excluded. When those computation times are included, the increase becomes below 10%. The proposed method thus does not need distinct computation increase.

#### 5. CONCLUSION

In this paper, we propose a method to calculate the equivalent waveform to crosstalk-induced noisy waveform. The proposed method does not evaluate the amount of delay variation at any points in a circuit. The effects of crosstalk noise are captured in the equivalent waveform. In order to consider the behavior of the receiver gate, we improve a least-square fitting technique with weighting coefficient for equivalent waveform derivation. We experimentally verify the proposed fitting method. Compared with the conventional methods that evaluate the delay variation at the interconnect end, the accuracy of the proposed method is much improved. The proposed method estimates both the maximum delay variation and its crosstalk-induced timing accurately. The proposed method does not require any additional characterization in cell library generation and does not increase computational cost so much in static timing analysis.

#### 6. REFERENCES

- K. Agarwal, Y. Cao, T. Sato, D. Sylvester and C. Hu, "Efficient Generation of Delay Change Curves for Noise-Aware Static Timing Analysis," *Proc. ASP-DAC*, pp.77-84, 2002.

- [2] Y. Sasaki and G. D. Micheli, "Crosstalk Delay Analysis using Relative Window Method," *Proc. ASIC/SOC Conference*, pp.9-13, 1999.

- [3] F. Dartu, L. T. Pileggi, "Calculating Worst-Case Gate Delays Due to Dominant Capacitance Coupling," *Proc. DAC*, pp. 46–51, 1997.

- [4] P. D. Gross, R. Arunachalam, K. Rajagopal and L. T. Pileggi, "Determination of Worst-Case Aggressor Alignment for Delay Calculation," *Proc. ICCAD*, pp.212-219, 1998.

- [5] S. Sirichotiyakul, D. Blaauw, C. Oh, R. Levy, V. Zolotov and J. Zuo, "Driver Modeling and Alignment for Worst-Case Delay Noise," *Proc. DAC*, pp.720-725, 2001.

- [6] M. Takahashi, M. Hashimoto and H. Onodera, "Crosstalk Noise Estimation for Generic RC Trees," *Proc. ICCD*, pp.110-116, 2001.

- [7] F. Chang, C. Chen, P. Sabramaniam, "An Accurate and Efficient Gate Level Delay Calculator for MOS Circuits," *Proc. DAC*, pp. 282–287, 1988.

- [8] B. N. Sheehan, "Predicting Coupled Noise in RC Circuits By Matching 1, 2, and 3 Moments," *Proc. DAC*, pp.532-535, 2000

- [9] A. Vittal, L. Chen, M. Marek-Sadowska, K.-P. Wang, and S. Yang, "Crosstalk in VLSI Interconnections," *IEEE Trans. CAD*, Vol. 18, pp.1817-1824, 1999.