# PREDICTMOS MOSFET Model and its Application to Submicron CMOS Inverter Delay Analysis

A.B. Bhattacharyya

Shrutin Ulman

Department of Physics,

Goa University,

Taleigao – Plateau, Goa 403206.

India.

abbhattacharya@unigoa.ernet.in

shrutin@unigoa.ernet.in

## **Abstract**

Predictive delay analysis is presented for a representative CMOS inverter with submicron device size using PREDICTMOS MOSFET model. As against SPICE, which adopts a time consuming numerical approach and relies more on empirical fitting of parameters for short channel devices, the predictive MOSFET model used is relatively simple and can be related to process and layout data with potential of estimation of the performance of a scaled design. The submicron CMOS inverter delay estimation under various loading and operative conditions have been compared against two benchmarks (a) Computer aided simulation with SPICE level 3 and (b) The analytical results of the Alpha Power Law based model. It is concluded that the PREDICTMOS model is potentially promising as a predictive analytic tool for submicron level design with transparency of device or circuit physics and an acceptable level of accuracy.

# 1. Introduction:

As the minimum feature size continues to decrease and the device count increases, it is increasingly realized by VLSI designers that simulators such as SPICE which are developed around numerical techniques are too slow for large scale designs. The problem gets further aggravated as the device model parameters for MOS transistors get more and more complex and empirical.

Though the CMOS gate / inverter transient characteristics, which are of primary interest to the VLSI designers, have been known through the analytical approach from the very early stage [1], the results are based on the early understanding of the

device model. The lack of an accurate and manageable physical models for short channel devices and the domination of simulation based design methodology have resulted in the loss of physical insight into the dynamics of the CMOS switch based subcircuits and systems.

The basic difficulty of analytic handling of the CMOS devices with small geometry features has been the choice of an acceptable physical model. Shoji [2] was perhaps the first to address the design issues of primitive short channel CMOS cells analytically. The present day scaling of the MOS device at the submicron level, however, demands much higher degree of authenticity of modeling than that used by Shoji. Alpha (α or n) power law by Sakurai and Newton introduced an empirical approach to account for velocity saturation characteristics of scaled MOSTs of submicron feature size [3]. Though in the last few years alpha power model has been used with some degree of success in the analytical characterization of short channel submicron CMOS inverters and circuits with varying degrees of complexity and operating conditions such as step and ramp response with capacitive load neglecting PMOS current contribution [4], ramp response with gate - drain coupling capacitance [5], transient response including PMOS load current [6] switching delay with RC [7], and CRC interconnect [8] model, series connected gates [9], generalised delay estimation [10] etc, the approach survives with the limitation of being totally empirical denying the possibility of exploring the potential of scaled design. Further, the alpha power model does not meet the demanding requirement of analog design. There has been some effort to find a correspondence between the alpha power model parameters and physical / technological entities of the device but it is at best an afterthought and does not have a natural physical basis.[11]

Briefly, there is a strong case for exploring a compact physical model which should be as cute and simple as the original quadratic model of MOS transistors, even in the presence of short channel effects such as velocity saturation, gate voltage dependent mobility degradation, channel length modulation, drain induced barrier lowering, etc. which characterize modern submicron and deep devices so that an analytical design submicron approach of basic analog and digital cells can be adopted keeping intact the transparency of the intrinsic device and circuit physics. Apart from the benefits of scalability such a model would be useful for developing physically meaningful delay and timing simulators with submicron devices.

The present work reports some initial exploratory results related to delay studies of short channel CMOS inverters with submicron feature size using a physics based predictive compact model – PREDICTMOS[15]. The investigation demonstrates that the model could provide an analytical base for large signal analysis of digital design with a strong link to process and layout parameters, keeping intact the physical insight during circuit simulation. The results indicate an acceptable level of accuracy over a wide range of loading and tranisent conditions.

The scope of the present work is confined to the demonstration of the predictive potential of PREDICTMOS model in digital design through a few representative delay studies of primitive CMOS cells with typical interconnect and loading conditions. The analysis presented is without considering the role of PMOS load current and gate - drain coupling. It may however be mentioned that the above simplifications do not reflect a limitation of the PREDICTMOS analytical capability and have been adopted solely for a simplified presentation of the results.

The results with the PREDICTMOS model have been compared with two benchmarks selected: Alpha Power law analytical approach and the SPICE 3 circuit simulations.

Section 2 presents the essential features of PREDICTMOS and Alpha Power models. Section 3 gives the outline of the formulation for the delay analysis with final expressions of delay parameters. Section 4 gives the graphs and tables demonstrating the capability of PREDICTMOS based analysis. Section 5 summarizes the conclusion of the study.

## 2. MOSFET Model:

# 2.1 The PREDICTMOS Model:[15]

The current – voltage equation of small geometry CMOS transistor in PRDEICTMOS is given by the

following relationship taking into account the velocity saturation, variation of the depletion channel width along the channel, channel length modulation, gate voltage dependent surface mobility, etc.:

$$I_{d} = 0 \qquad \text{for} \qquad V_{gs} < V_{T}$$

$$I_{d}_{in} = \left[\frac{\mu_{s}WCox}{L + \frac{\mu_{s}}{v_{s}}V_{ds}}\right] \left(V_{gs} - V_{T} - \frac{\alpha_{i}}{2}V_{ds}\right)V_{ds} \qquad \text{for } V_{ds} < V_{dsat} \qquad (1)$$

$$I_{d}_{sat} = \left[\frac{\mu_{s}WCox}{L + \frac{\mu_{s}}{v_{s}}V_{ds}}\right] \left[\left(V_{gs} - V_{T} - \frac{\alpha_{i}}{2}V_{dsat}\right)V_{dsat} + \left(V_{gs} - V_{T} - \alpha_{i}V_{dsat}\right)\left(V_{ds} - V_{dsat}\right)\right]$$

$$V_{\text{deat}} = \left[ \left( \frac{V_{\text{ge}} + LE_{\text{p}}}{\frac{E_{\text{p}}}{E_{\text{c}}} - 1} \right) \right] \sqrt{\frac{1 + 2V_{\text{ge}}LE_{\text{p}} \left( \frac{E_{\text{p}}}{E_{\text{c}}} - 1 \right)}{\left( V_{\text{ge}} + LE_{\text{p}} \right)^{2}} - 1}$$

$$\alpha_{i} = 1 + \frac{0.5k_{\text{eff}}}{\sqrt{\phi_{i} + V_{\text{sb}}}} \left[ 1 - \frac{1}{a_{1} + a_{2} \left( \phi_{i} + V_{\text{sb}} \right)} \right]$$

$$\mu_{s} = \frac{\mu_{o}}{1 + \theta \left( V_{\text{gs}} - V_{\text{T}} \right) + 2k_{\text{eff}} \theta \sqrt{\phi_{i} + V_{\text{sb}}}}$$

(2c)

where  $a_1=1.744$  and  $a_2=0.8364$ . for short channel devices, Equations (2a), (2b) and (2c) get into the PREDICTMOS model expression due to the considerations of the (a) velocity saturation effect due to the high electric field along the channel, (b) the bulk charge variation along the channel, and (c) gate voltage dependent mobility degradation. Cox is gate oxide capacitance per unit area,  $\mu_s$  is the surface mobility,  $\nu_s$  is the saturation velocity of the carrier mobility, W is the effective channel width, L is the effective channel length, V<sub>ge</sub> is the effective gate voltage,  $V_{ds}$  is applied voltage between the drain and source and  $V_{gs}$  is the applied voltage between the gate and the source, keff is the effective substrate factor, Ec is the critical electric field, E<sub>p</sub> is the geometry independent electric field at the saturation point,  $\varphi_i$  is the surface potential for the onset of strong inversion,  $V_{dsat}$  is the

drain saturation voltage, Idsat and Idlin are the currents in the saturation and linear regions respectively and V<sub>sb</sub> is the applied bias between the source and the bulk.

# Alpha Power Model:

As the results of PREDICTMOS have been compared with those obtained from the use of the alpha power law model. The Alpha Power law model is also mentioned for the sake of completeness and ready comparison. The I-V relationship is empirically assumed as [4]:

$$\begin{array}{lll} Id\!=\!0\;, & V_{gs}\!<\!V_{T} & (3) \\ Id\!=\!K_{1}\!(V_{gs}\!\!-\!\!V_{T}\!)^{\alpha\prime2}V_{ds}, & V_{ds}\!<\!V_{dsat} & (4) \\ Id\!=\!K_{s}\!(V_{gs}\!\!-\!\!V_{T}\!)^{\alpha}\;, & V_{ds}\!>\!=\!V_{dsat} & (5) \\ \end{array}$$

$$Id=K_1(V_{gs}-V_T)^{\alpha/2}V_{ds}, \qquad V_{ds} < V_{dsat}$$

(4)

$$Id=K_s(V_{gs}-V_T)^{\alpha}, \qquad V_{ds}>=V_{dsat}$$

(5)

where  $\alpha$  is the velocity saturation index and  $K_1$  and  $K_s$  are technology parameters. It is to be noted that  $\alpha$  is dependent on the degree of velocity saturation to be derived empirically and the conductance parameters K<sub>1</sub> and K<sub>s</sub> are technology and device size dependent. They have however no direct physical basis.

PREDICTMOS uses the conventional approach of calculating the inversion charge in the region where the gradual channel approximation (GCA) is valid. In the high field region where the GCA fails and the gate progressively loses control over the channel a box approximation is assumed for the channel charge. .The continuity of charge between the GCA and non-GCA region preserved at the boundary. The current is computed by standard drift current formulation. As can be seen from the equation (2) the approach does not require the calculation of the modulation of electric channel length  $\Delta L$  but elegantly accounts for the finite conductance of the device output through the drop of excess voltage  $(V_{ds} - V_{dsat})$  on the high field region. The gate voltage dependence on mobility, geometry and bias dependence of the threshold voltage V<sub>T</sub> can be easily incorporated. All the parameters involved are physical and scalability potential is built-in.

Alpha Power model on the other hand requires an empirical fitting of parameters such as  $\alpha$ .  $K_1$  and  $K_2$ to match the device characteristics. In short, where the Alpha Power lays emphasis on "fitting" with an analytically amenable simple form of the characterizing equation, the PREDICTMOS model is concerned with "predictability" without compromising on the parameters related to short channel MOS physics and the simplicity of the form.

#### 3. Propagation Delay with Ramp Input Waveform:

3.1 Delay Estimation with Capacitive Load:

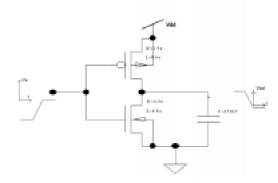

For transient analysis of the CMOS inverter as shown in the Fig. 1, we have considered the case of a ramp input which is a realistic description of the driving signal. For fast input ramps the effect of the PMOS on the delay can be neglected. This approximation is considered valid if the input slope exceeds one third the output slope, which normally happens in VLSI circuits, [4]. We shall make use of standard expression for the delay given by:

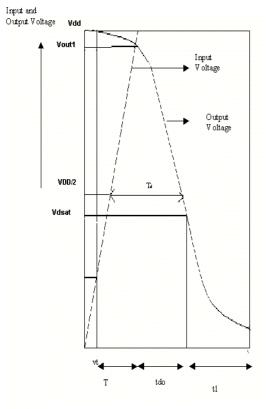

$$T_{d} = t_{0.5} - \frac{T}{2} \tag{6}$$

where  $T_d$  is the propagation delay,  $t_{0.5}$  is the time at which the output voltage drops to V<sub>dd</sub>/2 and T is the input rise time as depicted in Fig. 2.

The transeint behavior of the circuit in Figure 1 is obtained using the following differential equation:

$$\frac{dV_{\text{out}}}{dt} = \frac{-I_{\text{ds}}}{C_{\text{T}}} \tag{7}$$

where I<sub>ds</sub> is the drain to source current and depending on the state of operation of the transistor, Idlin or Idsat may be obtained from equation (1) and equation (2) respectively. Equation (7) is not solvable with the form of equations that describe the current and therefore some of the expressions have to be recast in an appropriate form to make the equation (7) amenable to analytical solution. We only outline below the steps involved as the details are outside the scope of the present paper.

PREDICTMOS Delay :The calculation propagation delay involves the following steps:

- Step 1: Linearization of the function  $V_{dsat}$  which has nonlinear dependence on  $(V_{gs} -$

- Step 2: Estimation of  $V_{out1}$  which is the value of output voltage when the input voltage reaches V<sub>dd</sub>.

- Step 3: Calculation of  $t_{do}$  the time for which the NMOST is in saturation after the input has reached  $V_{dd}$  as shown in Fig. 2.

- Step 4: The calculation of t<sub>1</sub>, the time for which the NMOST operates in the linear region.

- Step 5: The limits of integration are between  $V_{out1}$  and  $0.5V_{dd.}$

With the implementation of the above steps and some straightforward manipulation an analytical expression for the delay, as defined in equation (6), is obtained which is given below:

$$\begin{split} T_{4} &= \frac{T}{2} + \left(\frac{C_{L}}{a}\right) \left[\left(\frac{iV_{max}}{g} + \frac{-6 + gh + gL \ln |f \cdot gh + gV_{max}|}{g^{2}}\right)\right] - \\ &\left(\frac{C_{L}}{a}\right) \left[\left(\frac{iV_{gg}}{g} + \frac{-6 + gh + gL \ln |f \cdot gh + g\frac{V_{gg}}{g}|}{g^{2}}\right)\right] \end{split} \tag{8}$$

$$\begin{split} &\text{where, } a = \mu_s \ W \ Cox \ ; \ f \ = (V_{gs} \text{-} V_T \text{-} \alpha_i / 2 \ V_{dsat}) \ V_{dsat} \ ; \ g \\ &= (\ V_{gs} \text{-} V_T \text{-} \alpha_i / 2 \ V_{dsat}) \ ; \ h = V_{dsat} \ ; \ i \ = \alpha_i / 2 \ ; \end{split}$$

$v_t = V_T / V_{DD}$ , and  $C_L$  is the capacitive load.

It may be noted that the terms involved in the prediction of delay are related to physically meaningful parameters of device, process and layout. Alpha Power Delay: The expression for delay using the Alpha Power law is given by [4]:

$$T_{d} = \left(\frac{1}{2} - \frac{(1 - \upsilon_{t})}{(1 + \alpha)}\right)T + \frac{C_{L}V_{dd}}{2I_{do}}$$

(9)

where,  $I_{do}$  is the saturation current and the other symbols retain their meanings. It may be noted, that the expression for delay by Alpha Power model does not relate it with either the layout or process parameters. It may be further observed that both Alpha Power and PREDICTMOS based expressions for delay with capacitive load and ramp input maintain however, the same general form.

## 3.2 Delay Expression with RC Interconnect Load:

The delay expression for a CMOS inverter driving RC interconnect load using PREDICTMOS model is obtained by following the same steps as outlined above except that the limits of integration are between  $V_{\text{out2}}$  and (0.5  $V_{\text{dd}}$ ) which duly takes into account the shielding effect imposed by the interconnect resistance on the capacitive load to be seen by the inverter output [7]. Skipping the intermediate mathematical steps the final delay expression with PREDICTMOS model, is given by :

$$\begin{split} T_{d} &= \frac{T}{2} + \left(\frac{C_{L}}{a}\right) \left[\left(\frac{iV_{out}}{g} + \frac{-6 + ghi + gL \ln |f - gh + gV_{out}|}{g^{2}}\right)\right] - \\ &\left(\frac{C_{L}}{a}\right) \left[\left(\frac{i\left(\frac{V_{dd}}{2}\right)}{g} + \frac{-6 + ghi + gL \ln |f - gh + g\left(\frac{V_{dd}}{2}\right)|}{g^{2}}\right)\right] \end{split} \tag{10}$$

where R is the interconnect resistance between CMOS output node and the output capacitive load  $C_L$  and  $V_{out2}$  is the value of the output voltage when the input voltage reaches  $V_{dd}$ . The delay expression of an inverter driving a RC interconnect load is given by equation (8) of [7].

## 4. Discussion:

4.1 Propagation Delay with Varying Capacitive Load and Rise Time:

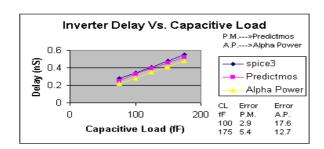

The delay was obtained using the PREDICTMOS, Alpha Power law and SPICE 3 for comparison and the results are shown through graphs and tables. All the analysis and simulations are done for  $0.6\mu$  CMOS inverter with W=0.9 $\mu$ , L=0.6 $\mu$  and V<sub>dd</sub>=5 volts. The figure 3 shows the change in propagation delay for

varying capacitive loads. It is found that PREDICTMOS accuracy is superior to Alpha Power for low capacitive loads.

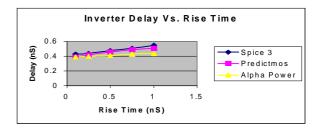

The table 1 shows the propagation delay for varying input rise times and a fixed capacitive load.

Table 1. Propagation Delay of a CMOS inverter Driving a Capacitive Load

| T    | $C_L$ | $T_d$ | $T_d$    | $T_d$       | Error      | Error         |

|------|-------|-------|----------|-------------|------------|---------------|

| (nS) | (f F) | spice | PREDICT  | (Alpha      | PREDICT    | (Alpha        |

|      |       | (nS)  | MOS (nS) | Power) (nS) | MOS<br>(%) | Power)<br>(%) |

| 0.1  | 150   | 0.43  | 0.39     | 0.39        | 9.3        | 9.3           |

| 0.25 | 150   | 0.44  | 0.42     | 0.4         | 4.5        | 9             |

| 0.5  | 150   | 0.48  | 0.46     | 0.41        | 4.1        | 14.5          |

| 0.75 | 150   | 0.51  | 0.49     | 0.43        | 3.9        | 15.6          |

| 1    | 150   | 0.55  | 0.51     | 0.44        | 7.2        | 20            |

It is observed that PREDICTMOS also leads to the conclusion that the propagation delay is less sensitive to input rise time compared to the capacitive load as given by SPICE and Alpha Power. An analysis of the results of Fig. 3 shows that PREDICTMOS model gives less error compared to the Alpha Power model on an average.

4.2 Propagation Delay with RC Interconnect:

Table 2 shows the propagation delay estimated by the PREDICTMOS model and Alpha Power model and their accuracy with respect to SPICE for a RC interconnect load for a few representative values of interconnect resistance for a fixed capacitive load.

Table 2. Propagation Delay of a 0.6μ CMOS Inverter Driving an R-C Interconnect

| R<br>Ω | T<br>nS | C <sub>L</sub><br>fF | SPICE<br>T <sub>d</sub><br>ns | PREDIC<br>TMOS<br>T <sub>d</sub><br>(ns) | Alpha Power T <sub>d</sub> (ns) | Error<br>PREDICT<br>MOS<br>(%) | Error<br>(Alpha Power)<br>(%) |

|--------|---------|----------------------|-------------------------------|------------------------------------------|---------------------------------|--------------------------------|-------------------------------|

| 100    | 0.5     | 150                  | 0.47                          | 0.45                                     | 0.4                             | 4.2                            | 14                            |

| 500    | 0.5     | 150                  | 0.41                          | 0.41                                     | 0.34                            | 0                              | 17                            |

| 1K     | 0.5     | 150                  | 0.35                          | 0.36                                     | 0.26                            | 2.8                            | 25                            |

It is seen that PREDICTMOS gives accuracy in delay prediction much superior to that of Alpha Power for RC interconnect load, with Spice 3 as reference.

## 5. Conclusions:

- PREDICTMOS a compact MOS model valid for submicron devices has been used for characterizing the delay parameters of a CMOS inverter with submicron feature size providing physically meaningful analytical expressions

- Though relatively simple cases have been illustrated with PREDICTMOS for delay

modeling of the CMOS inverter neglecting the contribution form the PMOS load and gate – drain coupling, a more generalized analysis, can be also implemented with the model. It can be shown that with generalization of the analysis without the above approximations the PREDICTMOS results match even closer with SPICE.

- The sample results given show that the PREDICTMOS model gives comparable accuracy relative to the Alpha Power model and has been found to require significantly less computational time compared to SPICE in circuit simulation.

- PREDICTMOS circuit modeling is scalable as the expressions involve parameters related to layout and process which is not possible with Alpha Power approach. PREDICTMOS uses significantly less number of model parameters than BSIM and provides acceptable accuracy for digital CMOS design. Though not a substitute for BSIM, the predictive and analytical feature capability PREDICTMOS have their own merits, advantages and applications.

- PREDICTMOS, in principle, has all the features for accurate analog circuit analysis making it suitable for mixed signal ASIC design.

- Results of more generalized considerations and specific applications are quite promising and under consideration for journal publication.

Acknowledgement: The work has been done as a part of the VLSI design program financially supported by Goa University and the All India Council for Technical Education. We shall like to thank Prof. B.S. Sonde, Prof. P.R. Sarode and Dr. A. Shirodkar for their keen interest, constant encouragement and sustained support in launching the VLSI design progam.

## References:

- [1] N.H.E. Weste and K. Eshraghian, Principles of CMOS VLSI design: A Systems Perspective, New York: McGraw Hill, 1993, pp.61–86.

- [2] M. Shoji, CMOS Digital Circuit Technology. N.J.: Prentice Hall, 1988.

- [3]T. Sakurai and A. R. Newton," A Simpel MOSFET model for circuit analyis", IEEE Transactions on Electron Devices, Vol. E.D.-38, No.4, April 1991, pp.887-894.

- Vol. E.D.-38, No.4, April 1991, pp.887-894. [4]T. Sakurai and A. R. Newton," Alpha Power law MOSFET model and its applications to CMOS inverter delay and other formulas", IEEE Journal of Solid-State Circuits, Vol.SC-25, No.2, April 1990, pp.584-594.

- [5] L. Bisdounis, S. Nikolaidis and O. Koufopavlou," Analytical Transient Response and Propagation Delay Estimation of the CMOS inverter for Short-Channel Devices", IEEE Journal of Solid-State Circuits, Vol. 33, No.2, Feb. 1998, pp. 302-306.

- [6] L. Bisdounis, S. Nikolaidis and O. Koufopavlou," Propagation Delay and Short Circuit Power Dissipation

- Modeling of the CMOS Inverter", IEEE Transactions on Circuits and Systems 1, Fundamental Theory and Applications, Vol. 45, No. 3, March 1998 pp. 259-270.

- [7] K. Tang and E.G.Friedman, "Transient Analysis of a CMOS inverter driving a R-C interconnect", National Science Foundation, N.Y., Research Publication. friedman@ee.rochester.edu

- [8]Akio Hirata et al," Analytical Formulas of Output Waveform and Short-Circuit Power Dissipation for Static CMOS Gates Driving a CRC  $\pi$  Load", IEICE Trans. Fundamentals, Vol. E00-A,No.1,January 1997, pp. 1-7.

- [9] T. Sakurai and A. R. Newton, "Delay Analysis of Series Connected MOSFET Circuits", IEEE Journal of Solid-State Circuits, Vol. 26, No. 2, February 1991, pp. 122-132.

- [10] Santanu Dutta, S.S. Mahant Shetti and S. L. Lusky, "A Comprehensive Delay Model for CMOS Inverters", IEEE Journal of Solid-State Circuits, Vol. 30, No. 8, August 1995, pp. 864-871.

- [11] Keith A. Bowman, B. L. Austin, J. C. Eble, Xinghai Tang and J. D. Meindl, "A Physical Alpha Power Law MOSFET Model", IEEE Journal of Solid State Circuits, Vol. 34, No. 10, October 1999, pp. 1410 1414.

- [12]V. Adler and E. G. Friedman," Delay and Power Expressions for a CMOS Inverter Driving a Resistive Capacitive Load", Analog Integrated Circuits and Signal Processing, Vol. 14, No.1, Sept. 1997, pp.29-39.

- [13]J.M. Daga and D. Auvergne," A Comprehensive Delay Macro-modeling for Submicrometer CMOS logics", IEEE Journal of Solid-State Circuits, Vol. 34, No.1, Jan. 1999.

- [14] F. Dartu and L.T. Pillegi, "Calculating Worst-Case Gate Delays due to Dominant Capacitance Coupling", Intel Corporation Research Article, 1997.

- [15] A. Klos and A. Kostka, "PREDICTMOS a Predictive Compact Model for Small Geometry MOSFETS for Circuit Simulation and Device Scaling Calculations", Solid State Electronics, Vol. 44, 2000, pp. 1145-1156.

Figure 1. CMOS Inverter

Figure 2. Inverter Operation Regions

Figure 3. Inverter Delay Vs. Capacitive Load

Figure 4. Inverter Delay Vs. Rise Time